i~.

83C152 HARDWARE DESCRIPTION

Figure4.11showsthe three tasksto whichthe internal

bus of the 8XC152can be dedicated.In this tigurq

Instruction Cycle means the completeexecutionof a

singleinstruction, whether it takes 1, 2 or 4 machine

cycles.DMA Cyclemeansthe transferof a singledata

bytefromsourceto destination,whetherit takes 1or 2

machinecycles.Eachtimea DMACycleor an Instruc-

tion Cycleis executed,on-chiparbitrationlogicdeter-

mineswhichtype of cycleis to be executednext.

Note that when an instructionis executed,if the in-

struction wrote to a DMA register(definedin Figure

4.1 but excludingPCON), tien snother instruction is

executedwithout further arbitration.Therefore,a sin-

gle write or a series of writes to DMA registers will

preventa DMAfromtakingpla% andwillcontinueto

prevent a DMA from taking place until at least one

instruction is executed which does not write to any

DMA register.

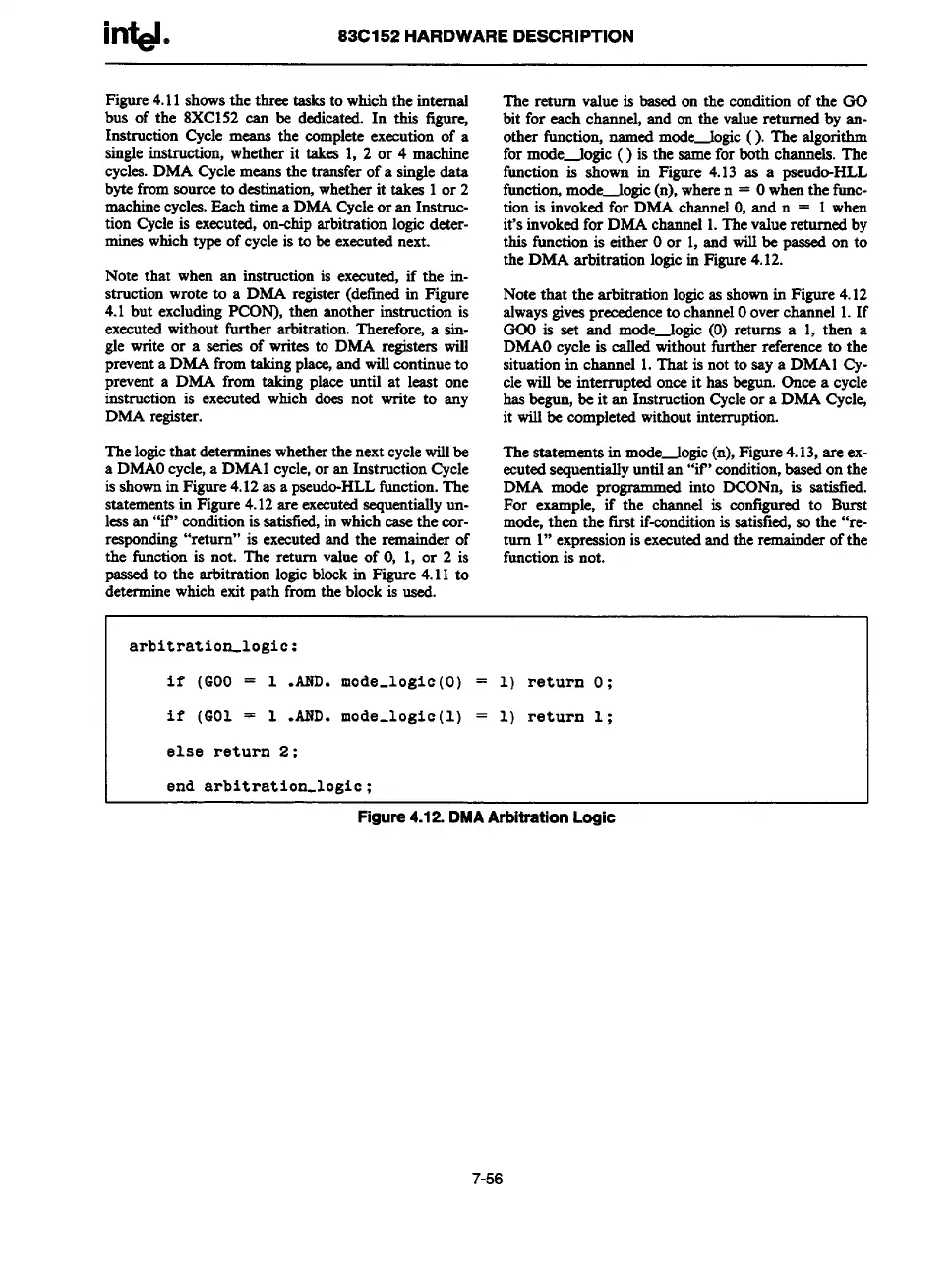

Thelogicthat determineswhetherthenextcyclewillbe

a DMAOcycle,a DMAI cycle,or an Instruction Cycle

isshownin Figure4,12as a pseudo-HLLfunction.The

statementsin Figure4.12are executedsequentiallyun-

lessan “it” conditionis sstisfi~ in whichcasethe cor-

responding“return” is executedand the remainder of

the function is not. The return value of O, 1, or 2 is

passedto the arbitration logicblockin Figure 4.11 to

detemninewhichexitpath fromthe blockis used.

The return value is basedon the conditionof the 00

bit for each channel,and onthe valuereturned by an-

other functio~ namedmodedogic (). The algorithm

for mode-logic () is the samefor both channels.The

function is shown in Figure 4.13 as a pseudo-HLL

functionjmode-logic (n),wheren = Owhenthe func-

tion is invokedfor DMA cbannelO,and n = 1 when

it’sinvokedfor DMA channel1.Thevaluereturnedby

this t%nctionis either Oor 1,and willbe passedon to

the DMA arbitration logicin Figure4.12.

Notethat the arbitrationlogicas shownin Figure4.12

alwaysgivesprecedenceto channelOoverchannel 1.If

000 is set and mode-logic (0) returns a 1, then a

DMAOcycleis called withouttiwtherreferenm to the

situationin channel 1.That is not to saya DMAI Cy-

cle willbe interrupted onceit has begun.Once a cycle

hasbegun,be it an InstructionCycleor a DMA Cycle,

it willbe completedwithoutinterruption.

Thestatements in modedogic (n),Figure4.13,are ex-

ecutedsequentiallyuntilan “if’ condition,basedonthe

DMA mode pro

grsmmed into DCONn, is sstistied.

For example, if the channel is configured to Burst

mode,then the first if-conditionis satisfied,so the “re-

turn 1“exrmssionis executedandthe remainderof

the

fimctioni; not.

arbitration-logic:

if (GOO= 1 .AND. mode-logic (0) = 1) return O;

if (GO1 = 1 .AND. modeJogic (1) = 1) return 1 ;

else return 2;

end arbitration-logic;

Figure 4.12. DMA Arbitration Logic

7-56

Loading...

Loading...