66

8331B–AVR–03/12

Atmel AVR XMEGA AU

Note:

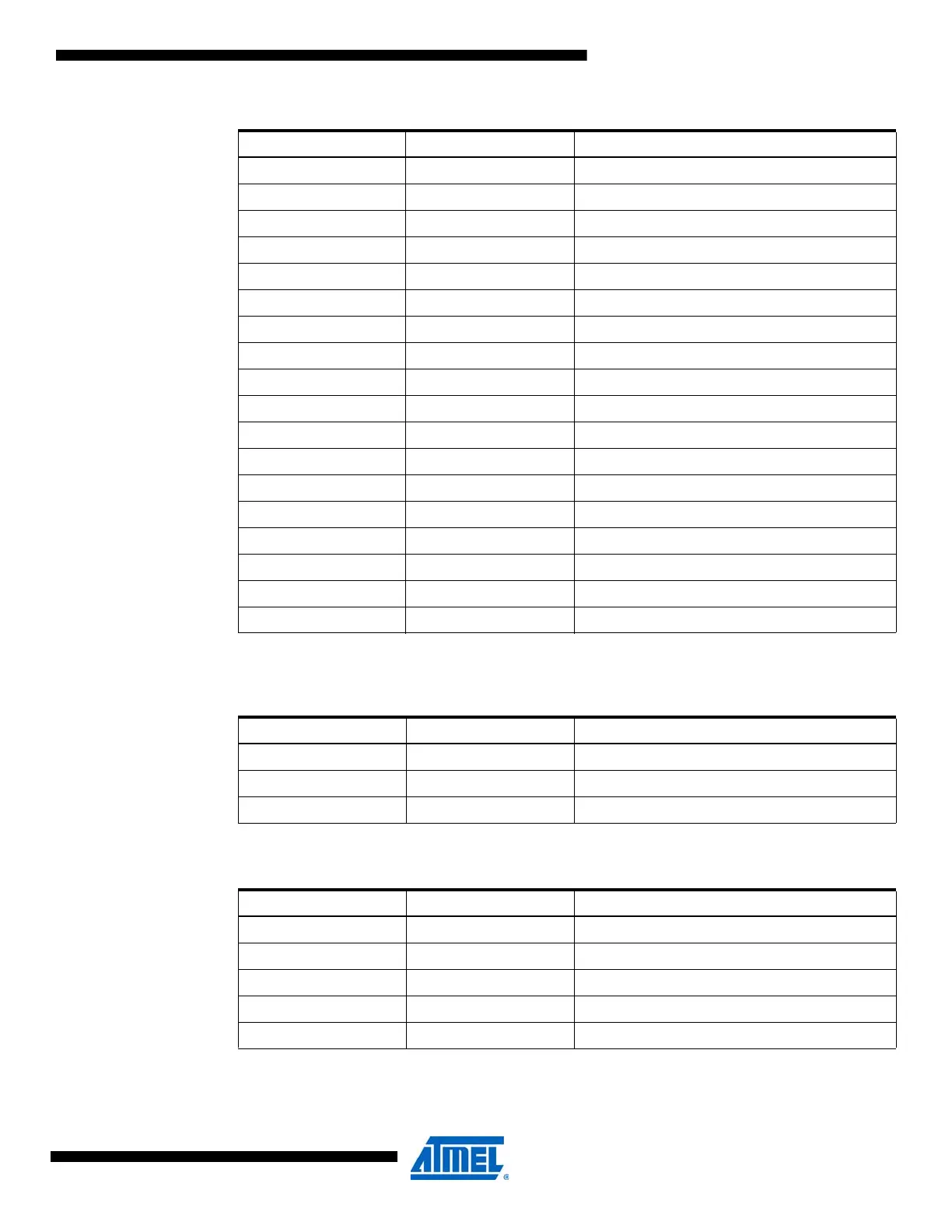

Notes: 1. For DAC only, channel 0 and 1 exists and can be used as triggers.

2. Channel 4 equals ADC channel 0 to 3 ORed together.

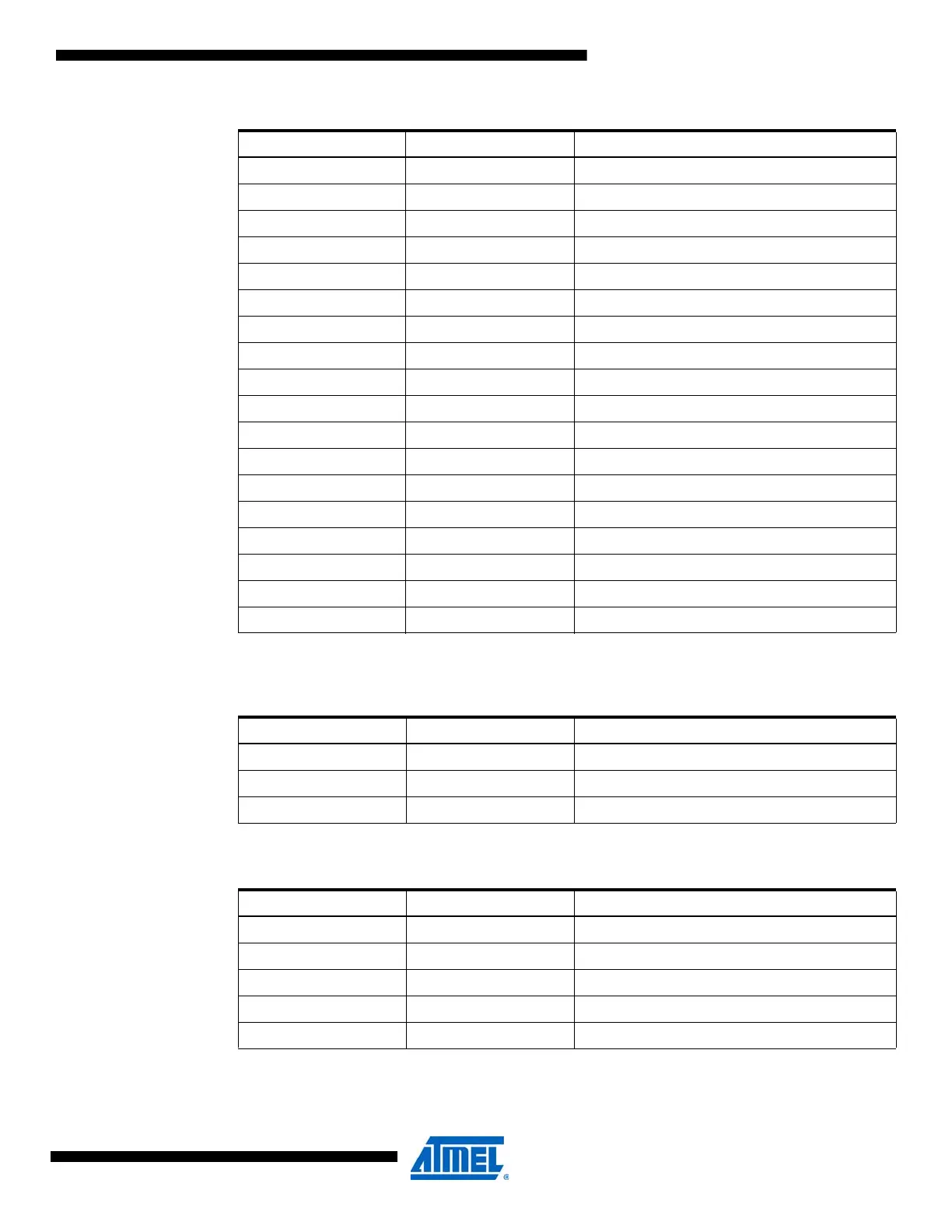

0x4A SPIC SPI C DMA triggers value

0x4B USARTC0 USART C0 DMA triggers base value

0x4E USARTC1 USART C1 DMA triggers base value

0x60 TCD0 Timer/counter D0 DMA triggers base value

0x66 TCD1 Timer/counter D1 triggers base value

0x6A SPID SPI D DMA triggers value

0x6B USARTD0 USART D0 DMA triggers base value

0x6E USARTD1 USART D1 DMA triggers base value

0x80 TCE0 Timer/counter E0 DMA triggers base value

0x86 TCE1 Timer/counter E1 triggers base value

0x8A SPIE SPI E DMA triggers value

0x8B USARTE0 USART E0 DMA triggers base value

0x8E USARTE1 USART E1 DMA triggers base value

0xA0 TCF0 Timer/counter F0 DMA triggers base value

0xA6 TCF1 Timer/counter F1 triggers base value

0xAA SPIF SPI F DMA trigger value

0xAB USARTF0 USART F0 DMA triggers base value

0xAE USARTF1 USART F1 DMA triggers base value

Table 5-10. DMA trigger source offset values for event system triggers.

TRGSRC Offset Value Group Configuration Description

+0x00 CH0 Event channel 0

+0x01 CH1 Event channel 1

+0x02 CH2 Event channel 2

Table 5-11. DMA trigger source offset values for DAC and ADC triggers.

TRGSRC offset value Group Configuration Description

+0x00 CH0 ADC/DAC channel 0

+0x01 CH1 ADC/DAC channel 1

+0x02 CH2

(1)

ADC channel 2

+0x03 CH3 ADC channel 3

+0x04 CH4

(2)

ADC channel 0, 1, 2, 3

Table 5-9. DMA trigger source base values for all modules and peripherals. (Continued)

TRIGSRC Base Value Group Configuration Description

Loading...

Loading...