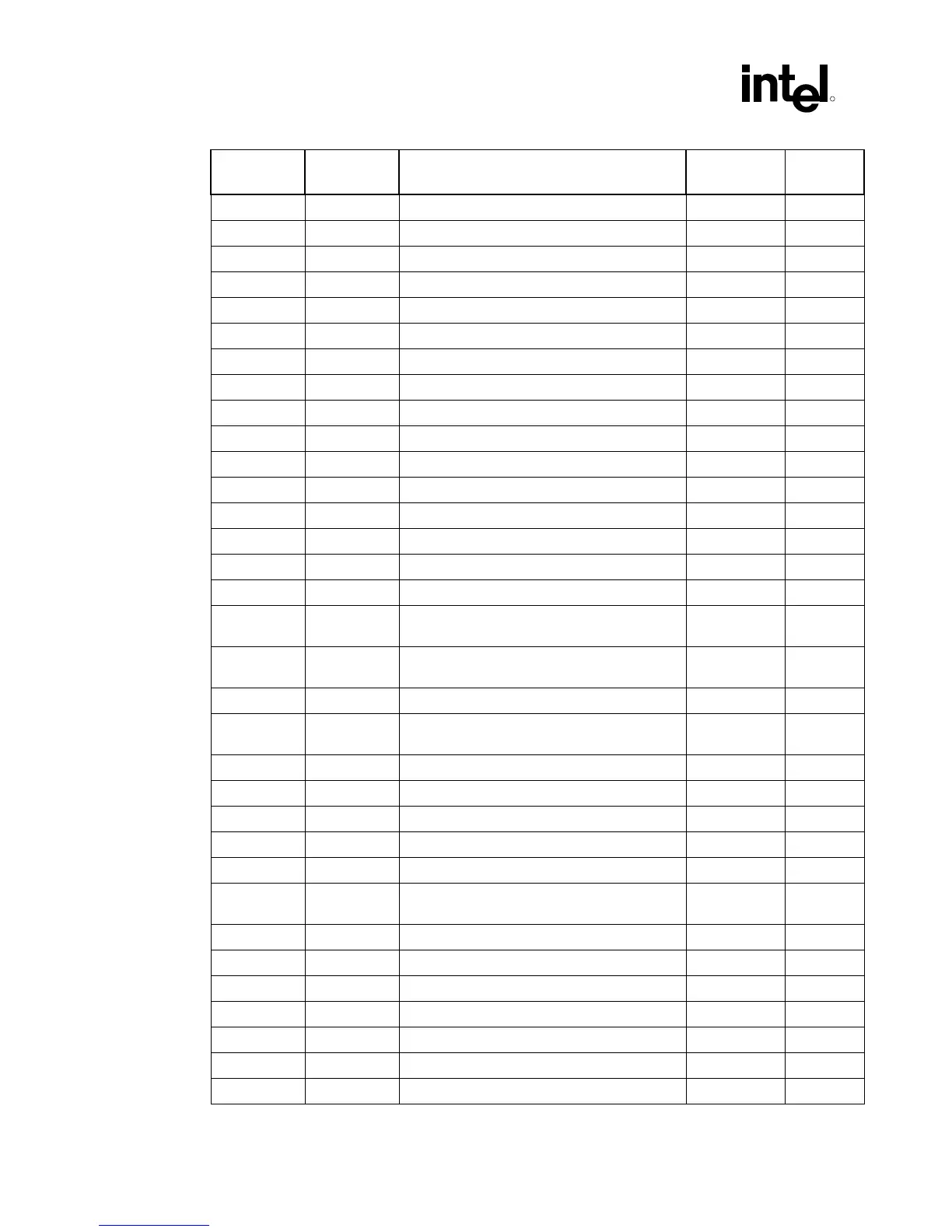

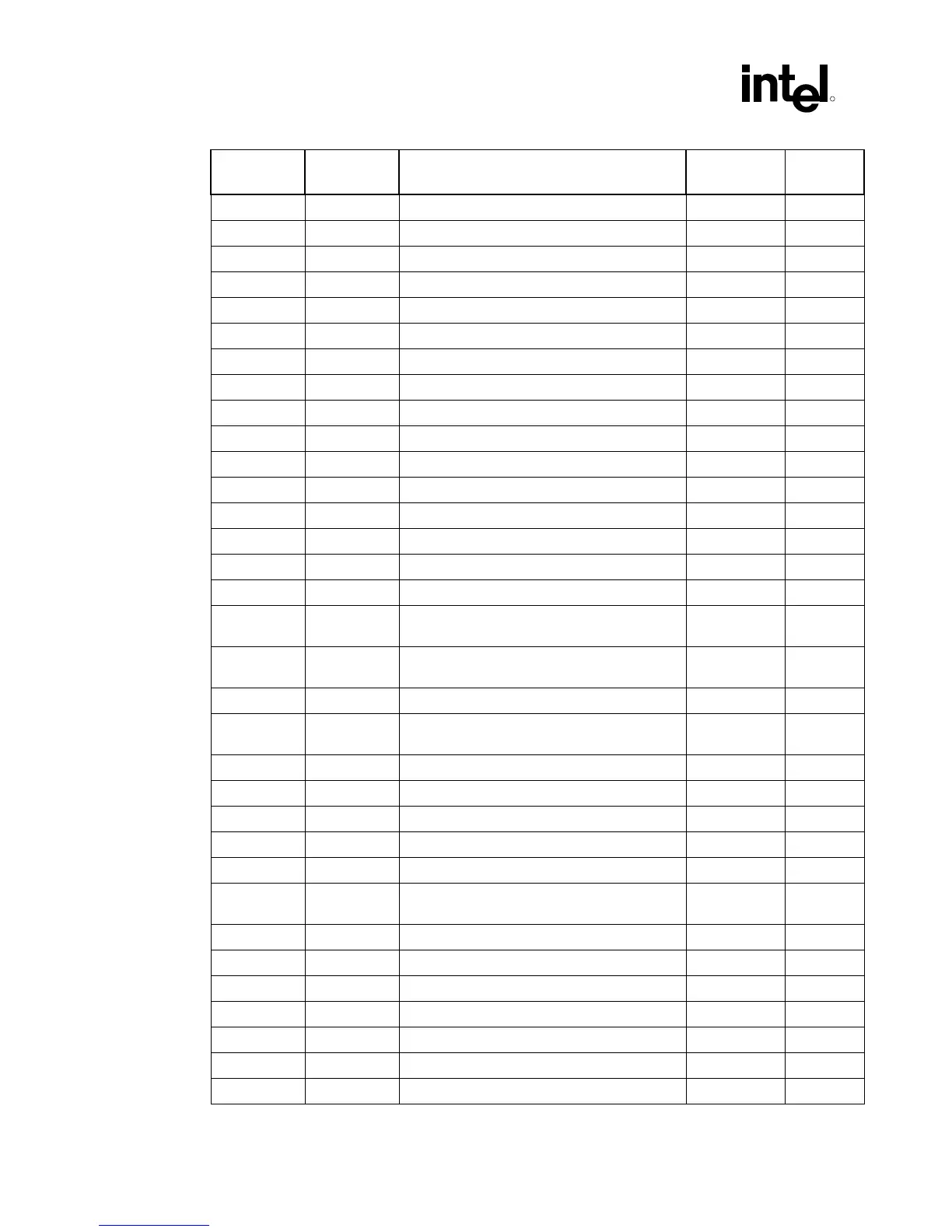

Host Bridge/DRAM Controller Registers (D0:F0)

R

46 Intel

®

82925X/82925XE MCH Datasheet

Address

Offset

Register

Symbol

Register Name

Default

Value

Access

52h–53h — Reserved — —

54h–57h DEVEN Device Enable 00000019h R/W

58h–5Bh DEAP DRAM Error Address Pointer 00000000h RO/S

5Ch DERRSYN DRAM Error Syndrome 00h RO/S

5Dh DERRDST DRAM Error Destination 00h RO/S

5Fh–8Fh — Reserved — —

90h PAM0 Programmable Attribute Map 0 00h R/W

91h PAM1 Programmable Attribute Map 1 00h R/W

92h PAM2 Programmable Attribute Map 2 00h R/W

93h PAM3 Programmable Attribute Map 3 00h R/W

94h PAM4 Programmable Attribute Map 4 00h R/W

95h PAM5 Programmable Attribute Map 5 00h R/W

96h PAM6 Programmable Attribute Map 6 00h R/W

97h LAC Legacy Access Control 00h R/W

98–9Bh — Reserved — —

9Ch TOLUD Top of Low Usable DRAM 08h R/W

9Dh SMRAM System Management RAM Control 00h RO,

R/W/L

9Eh ESMRAMC Extended System Management RAM Control 00h RO,

R/W/L

9F–C7h — Reserved — —

C8h–C9h ERRSTS Error Status 0000h RO,

R/W/L

CAh–CBh ERRCMD Error Command 0000h R/W

CCh—CDh SMICMD SMI Command 0000h R/W

CEh—CFh SCICMD SCI Command 0000h R/W

D0h–DBh — Reserved — —

DCh–DFh SKPD Scratchpad Data 00000000h R/W

E0h–E8h CAPID0 Capability Identifier 00000000000

1090009h

RO

E9h–FFh — Reserved — —

100h C0DRB0 Channel A DRAM Rank Boundary Address 0 00h R/W

101h C0DRB1 Channel A DRAM Rank Boundary Address 1 00h R/W

102h C0DRB2 Channel A DRAM Rank Boundary Address 2 00h R/W

103h C0DRB3 Channel A DRAM Rank Boundary Address 3 00h R/W

104h–107h — Reserved — —

108h C0DRA0 Channel A DRAM Rank 0,1 Attribute 00h R/W

Loading...

Loading...