UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 238 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

11.10.7.3 USB DMA Request Set register (USBDMARSet - 0x5000 C258)

Writing one to a bit in this register sets the corresponding bit in the USBDMARSt register.

Writing zero has no effect.

This register allows software to raise a DMA request. This can be useful when switching

from Slave to DMA mode of operation for an endpoint: if a packet to be processed in DMA

mode arrives before the corresponding bit of USBEpIntEn is cleared, the DMA request is

not raised by hardware. Software can then use this register to manually start the DMA

transfer.

Software can also use this register to initiate a DMA transfer to proactively fill an IN

endpoint buffer before an IN token packet is received from the host.

USBDMARSet is a write-only register.

The USBDMARSet bit allocation is identical to the USBDMARSt register (Table 222

).

11.10.7.4 USB UDCA Head register (USBUDCAH - 0x5000 C280)

The UDCA (USB Device Communication Area) Head register maintains the address

where the UDCA is located in the RAM. Refer to Section 11.15.2 “

USB device

communication area” and Section 11.15.4 “The DMA descriptor” for more details on the

UDCA and DMA descriptors. USBUDCAH is a read/write register.

11.10.7.5 USB EP DMA Status register (USBEpDMASt - 0x5000 C284)

Bits in this register indicate whether DMA operation is enabled for the corresponding

endpoint. A DMA transfer for an endpoint can start only if the corresponding bit is set in

this register. USBEpDMASt is a read-only register.

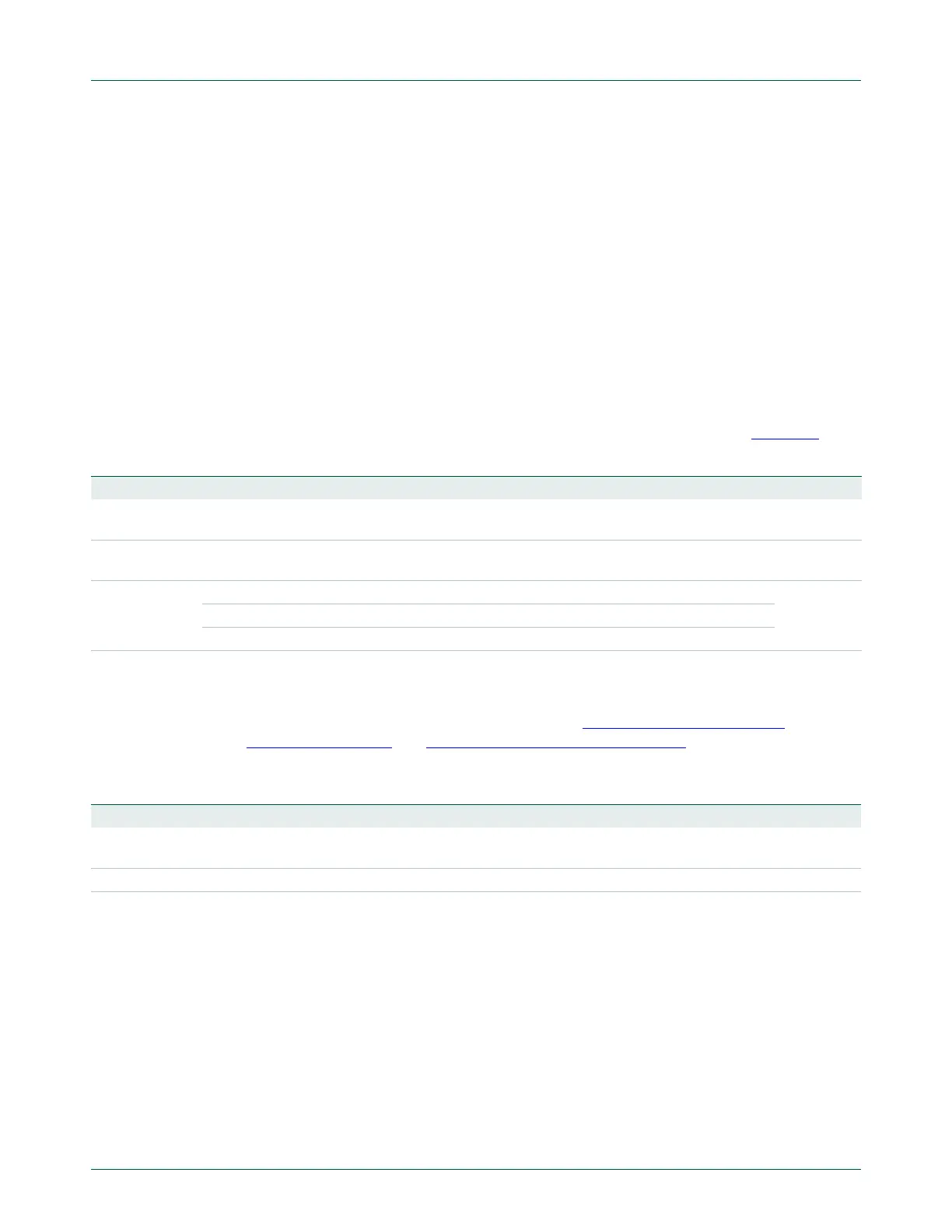

Table 225. USB DMA Request Set register (USBDMARSet - address 0x5000 C258) bit description

Bit Symbol Value Description Reset value

0 EP0 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and the EP0 bit

must be 0).

0

1 EP1 0 Control endpoint IN (DMA cannot be enabled for this endpoint and the EP1 bit must

be 0).

0

31:2 EPxx Set the endpoint xx (2

xx 31) DMA request. 0

0No effect.

1 Set the corresponding bit in USBDMARSt.

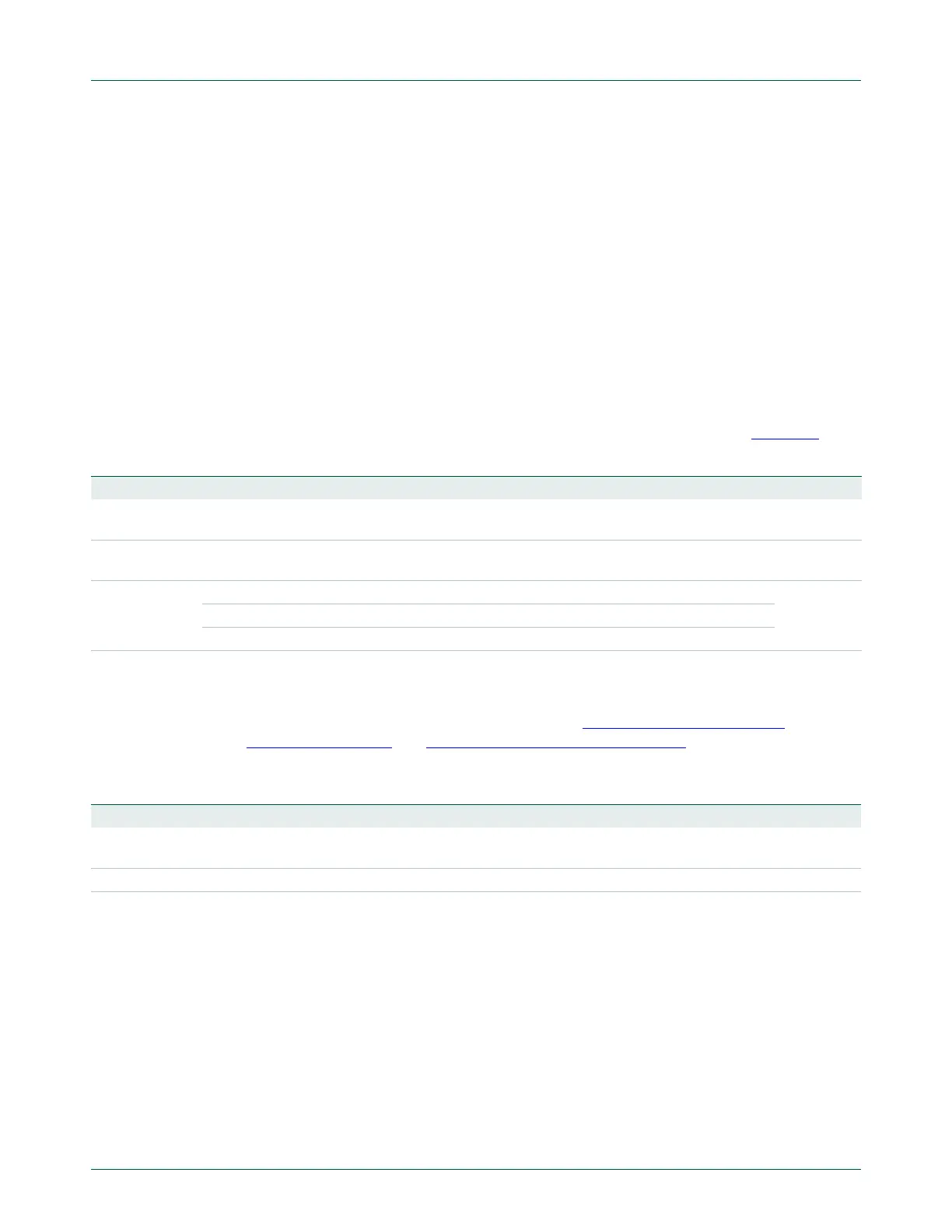

Table 226. USB UDCA Head register (USBUDCAH - address 0x5000 C280) bit description

Bit Symbol Description Reset value

6:0 - Reserved. Software should not write ones to reserved bits. The UDCA is aligned to

128-byte boundaries.

0x00

31:7 UDCA_ADDR Start address of the UDCA. 0

Loading...

Loading...