UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 772 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

When setting TBLOFF, you must align the offset to the number of exception entries in the

vector table. The recommended alignment is 256 words, allowing for 128 interrupts.

Remark: Table alignment requirements mean that bits[7:0] of the table offset are always

zero.

34.4.3.6 Application Interrupt and Reset Control Register

The AIRCR provides priority grouping control for the exception model, endian status for

data accesses, and reset control of the system. See the register summary in Table 654

and Table 659

for its attributes.

To write to this register, you must write

0x5FA

to the VECTKEY field, otherwise the

processor ignores the write.

The bit assignments are shown in Table 659

.

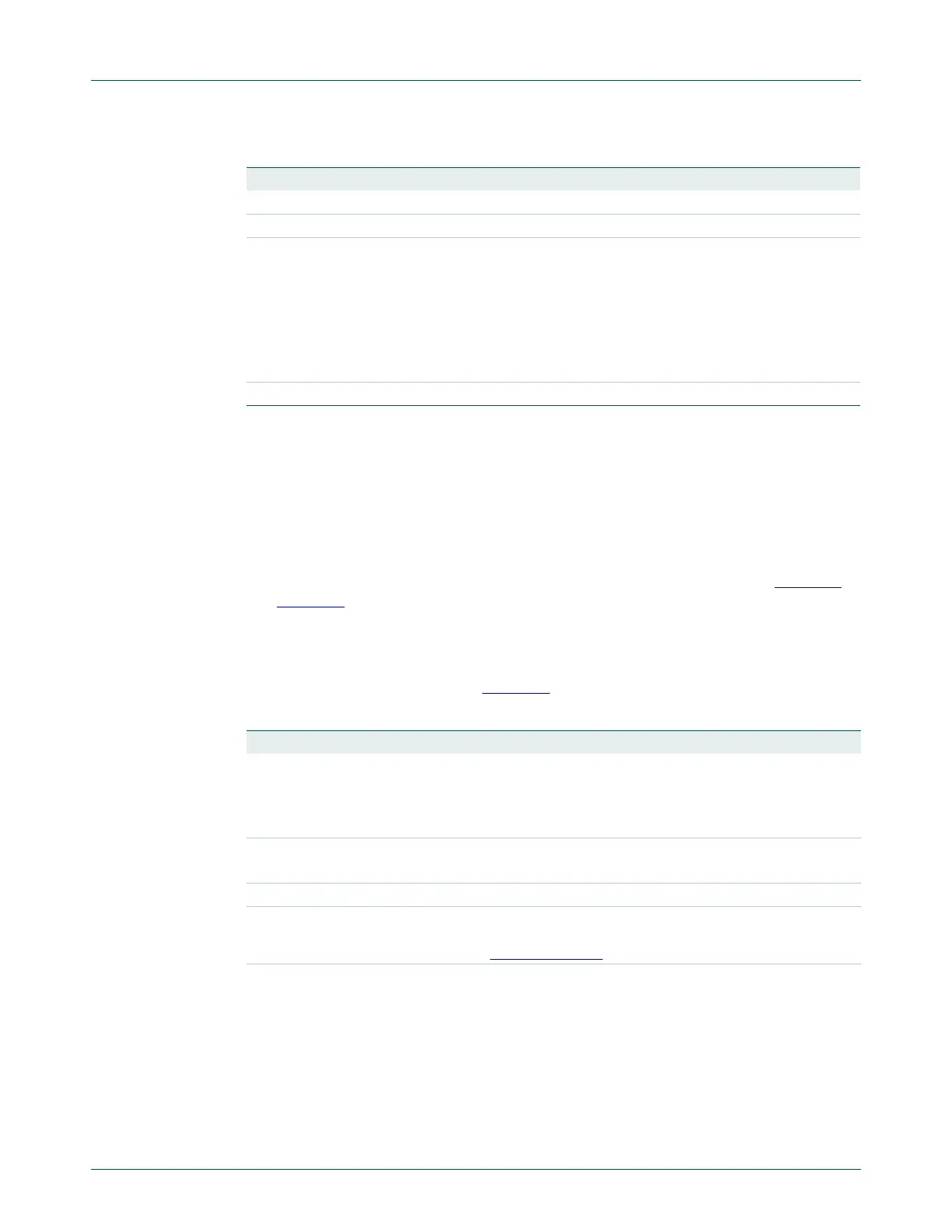

Table 658. VTOR bit assignments

Bits Name Function

[31:30] - Reserved.

[29:8] TBLOFF Vector table base offset field. It contains bits[29:8] of the offset of the table

base from the bottom of the memory map.

Remark: Bit[29] determines whether the vector table is in the code or

SRAM memory region:

Bit[29] is sometimes called the TBLBASE bit.

• 0 = code

• 1 = SRAM.

[7:0] - Reserved.

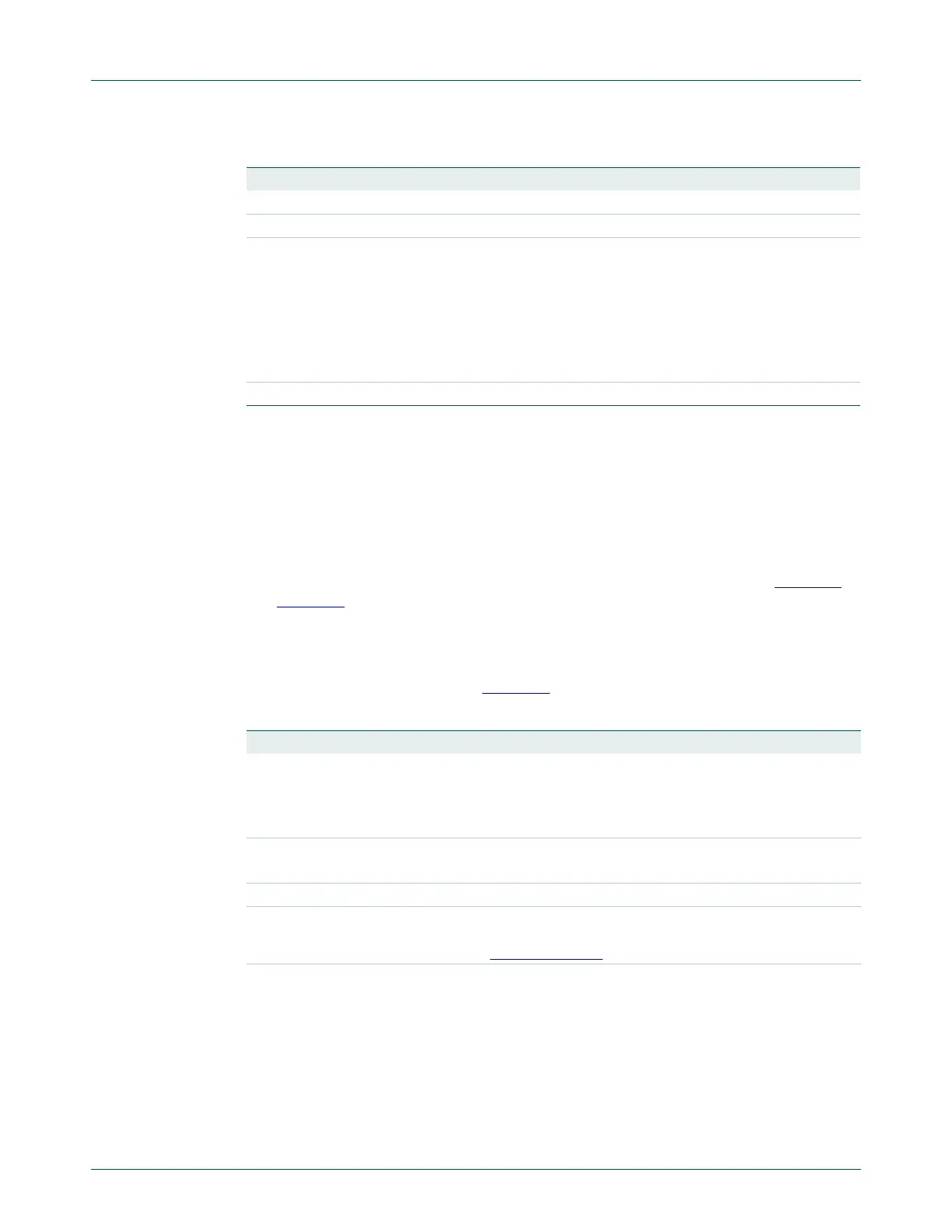

Table 659. AIRCR bit assignments

Bits Name Type Function

[31:16] Write:

VECTKEYSTAT

Read: VECTKEY

RW Register key:

Reads as

0x05FA

On writes, write

0x5FA

to VECTKEY, otherwise the write is

ignored.

[15] ENDIANESS RO Data endianness bit:

0 = Little-endian.

[14:11] - - Reserved

[10:8] PRIGROUP R/W Interrupt priority grouping field. This field determines the

split of group priority from subpriority, see

Section 34.4.3.6.1

.

[7:3] - - Reserved.

Loading...

Loading...