UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 503 of 841

NXP Semiconductors

UM10360

Chapter 22: LPC176x/5x Repetitive Interrupt Timer (RIT)

22.3.3 RI Control register (RICTRL - 0x400B 0008)

22.3.4 RI Counter register (RICOUNTER - 0x400B 000C)

22.4 RI timer operation

Following reset, the counter begins counting up from 00000000h. Whenever the counter

value equals the value programmed into the RICOMPVAL register the interrupt flag will be

set. Any bit or combination of bits can be removed from this comparison (i.e. forced to

compare) by writing a ‘1’ to the corresponding bit(s) in the RIMASK register. If the

enable_clr bit is low (default state), a valid comparison ONLY causes the interrupt flag to

be set. It has no effect on the count sequence. Counting continues as usual. When the

counter reaches FFFFFFFFh it rolls-over to 00000000h on the next clock and continues

counting. If the enable_clr bit is set to ‘1’ a valid comparison will also cause the counter to

be reset to zero. Counting will resume from there on the next clock edge.

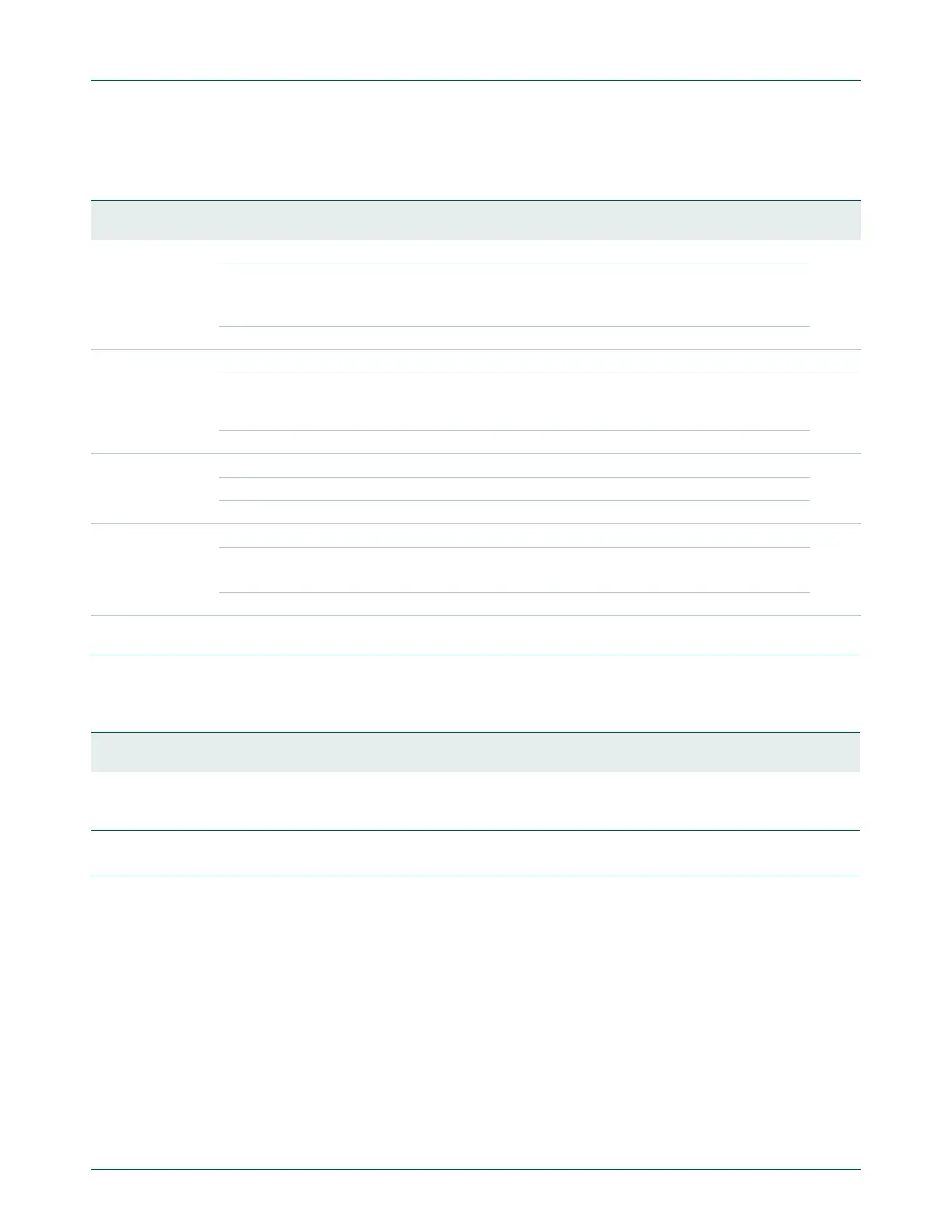

Table 436. RI Control register (RICTRL - address 0x400B 0008) bit description

Bit Symbol Value Description Reset

value

0 RITINT Interrupt flag 0

1 This bit is set to 1 by hardware whenever the counter value equals the masked

compare value specified by the contents of RICOMPVAL and RIMASK registers.

Writing a 1 to this bit will clear it to 0. Writing a 0 has no effect.

0 The counter value does not equal the masked compare value.

1 RITENCLR Timer enable clear

1 The timer will be cleared to 0 whenever the counter value equals the masked compare

value specified by the contents of RICOMPVAL and RIMASK registers. This will occur

on the same clock that sets the interrupt flag.

0

0 The timer will not be cleared to 0.

2 RITENBR Timer enable for debug 1

1 The timer is halted when the processor is halted for debugging.

0 Debug has no effect on the timer operation.

3 RITEN Timer enable. 1

1 Timer enabled.

Remark: This can be overruled by a debug halt if enabled in bit 2.

0 Timer disabled.

31:4 - - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

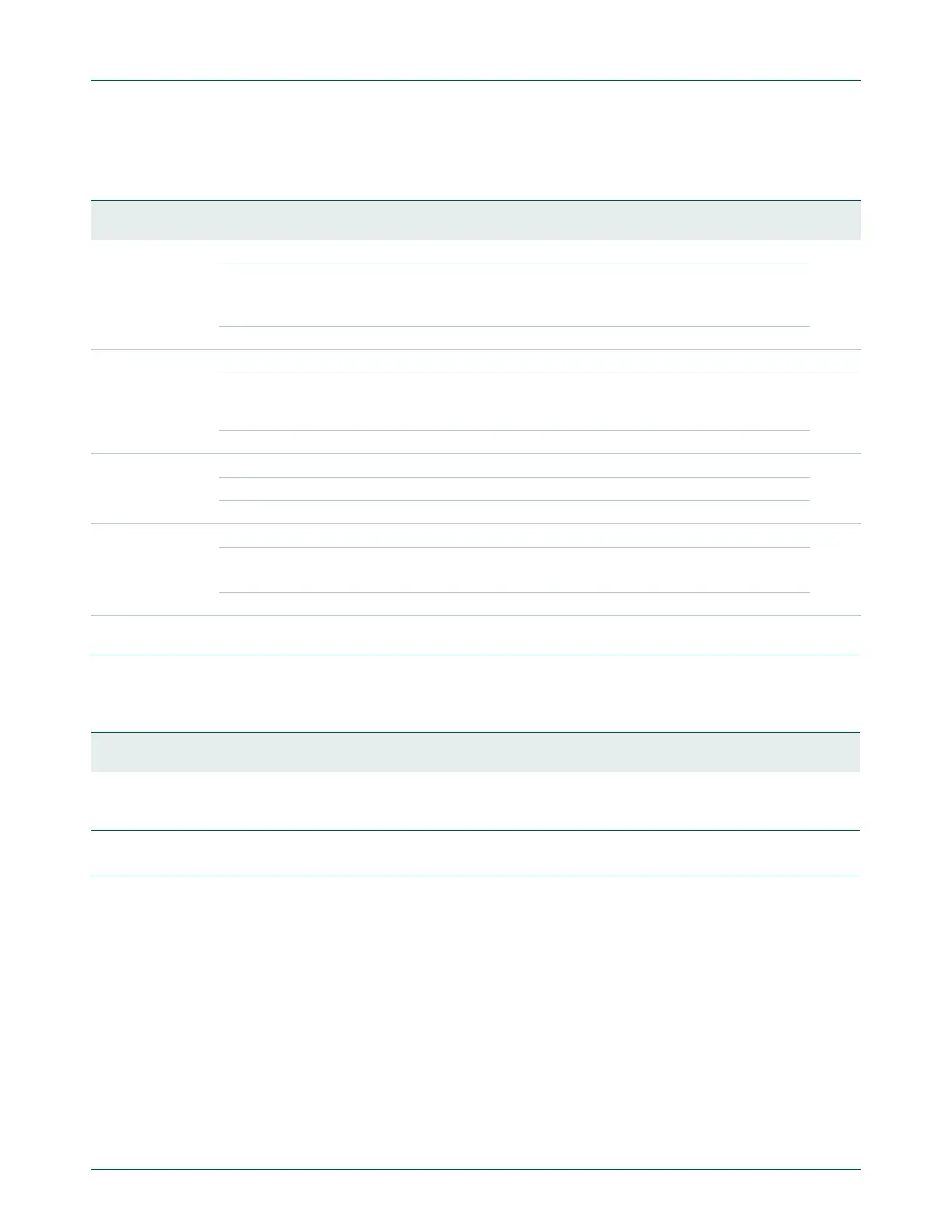

Table 437. RI Counter register (RICOUNTER - address 0x400B 000C) bit description

Bit Symbol Description Reset

value

31:0 RICOUNTER 32-bit up counter. Counts continuously unless RITEN bit in RICTRL register is cleared or

debug mode is entered (if enabled by the RITNEBR bit in RICTRL). Can be loaded to any

value in software.

0

Loading...

Loading...