UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 794 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.4.5.7 MPU mismatch

When an access violates the MPU permissions, the processor generates a memory

management fault, see Section 34.3.1.4 “

Exceptions and interrupts”. The MMFSR

indicates the cause of the fault. See Table 668

for more information.

34.4.5.8 Updating an MPU region

To update the attributes for an MPU region, update the RNR, RBAR and RASR registers.

You can program each register separately, or use a multiple-word write to program all of

these registers. You can use the RBAR and RASR aliases to program up to four regions

simultaneously using an

STM

instruction.

34.4.5.8.1 Updating an MPU region using separate words

Simple code to configure one region:

; R1 = region number

; R2 = size/enable

; R3 = attributes

; R4 = address

LDR R0,=MPU_RNR ; 0xE000ED98, MPU region number register

STR R1, [R0, #0x0] ; Region Number

STR R4, [R0, #0x4] ; Region Base Address

STRH R2, [R0, #0x8] ; Region Size and Enable

STRH R3, [R0, #0xA] ; Region Attribute

Disable a region before writing new region settings to the MPU if you have previously

enabled the region being changed. For example:

; R1 = region number

; R2 = size/enable

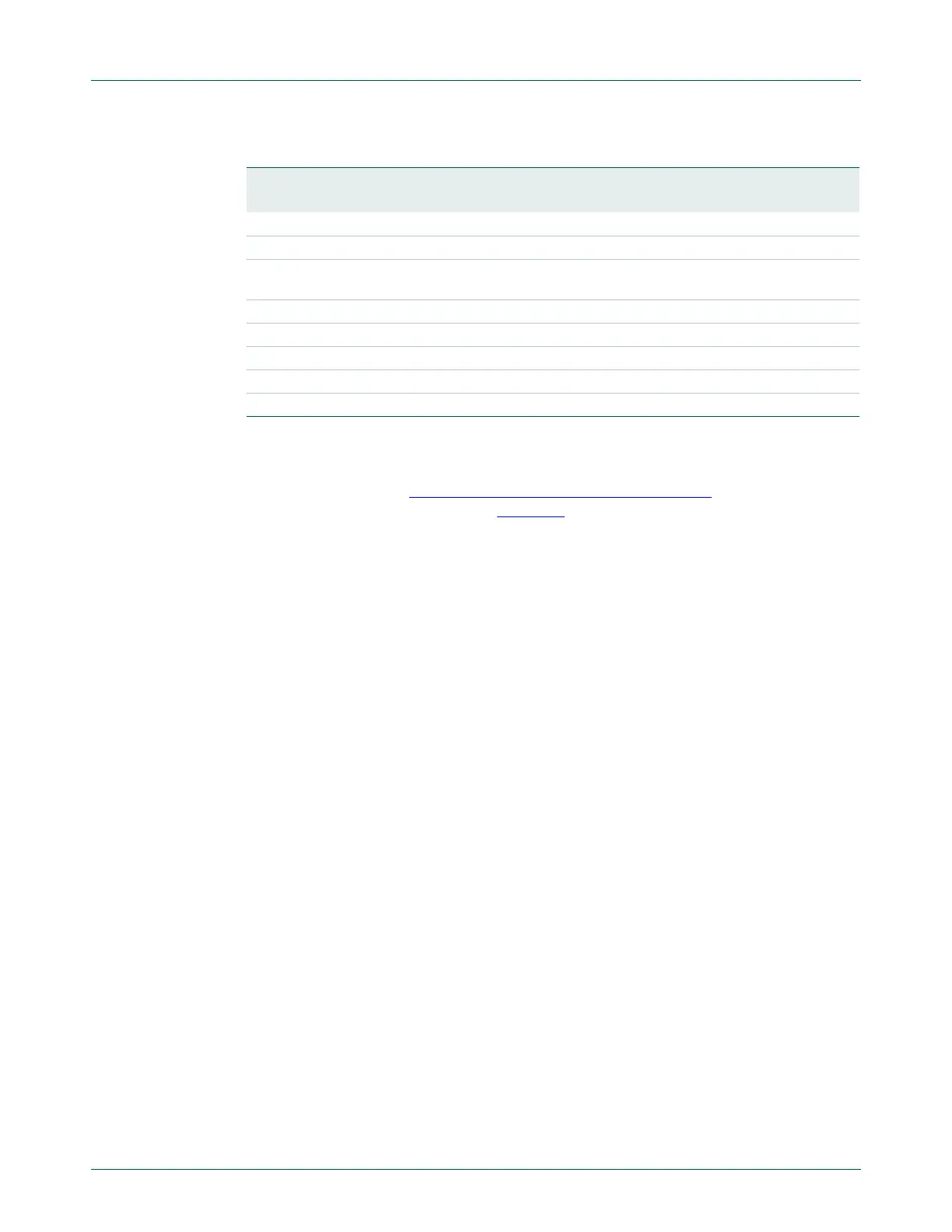

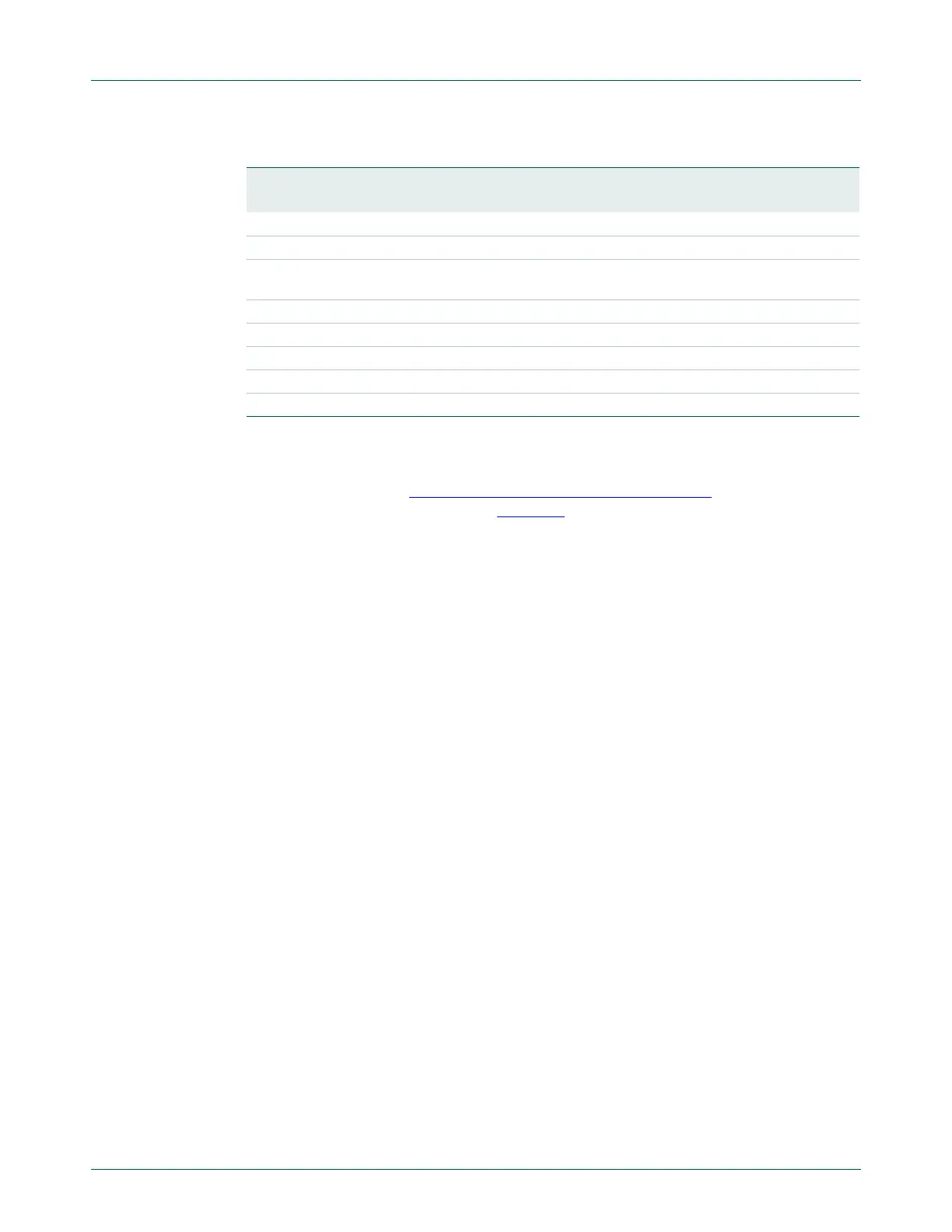

Table 689. AP encoding

AP[2:0] Privileged

permissions

Unprivileged

permissions

Description

000 No access No access All accesses generate a permission fault

001 RW No access Access from privileged software only

010 RW RO Writes by unprivileged software generate a

permission fault

011 RW RW Full access

100 Unpredictable Unpredictable Reserved

101 RO No access Reads by privileged software only

110 RO RO Read only, by privileged or unprivileged software

111 RO RO Read only, by privileged or unprivileged software

Loading...

Loading...