UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 346 of 841

NXP Semiconductors

UM10360

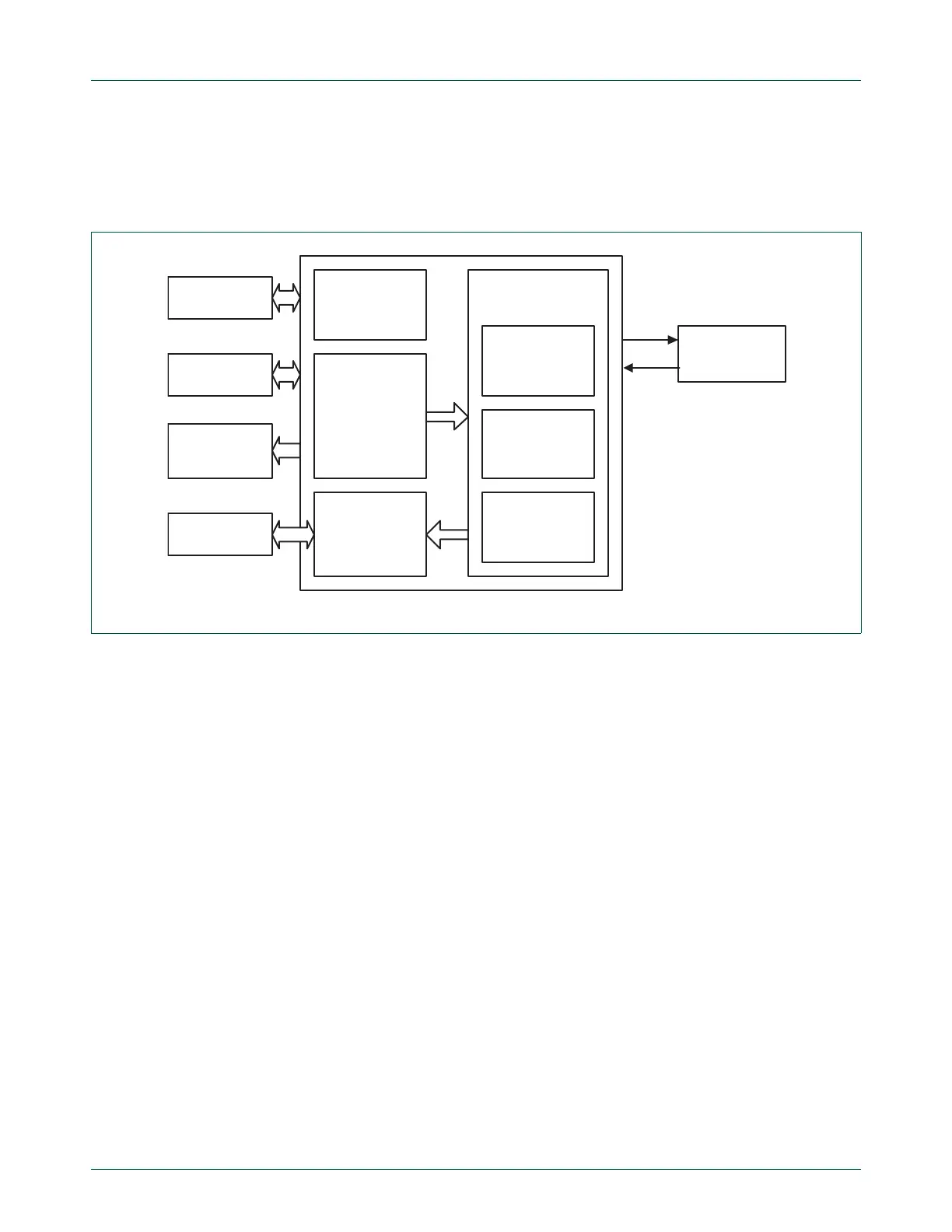

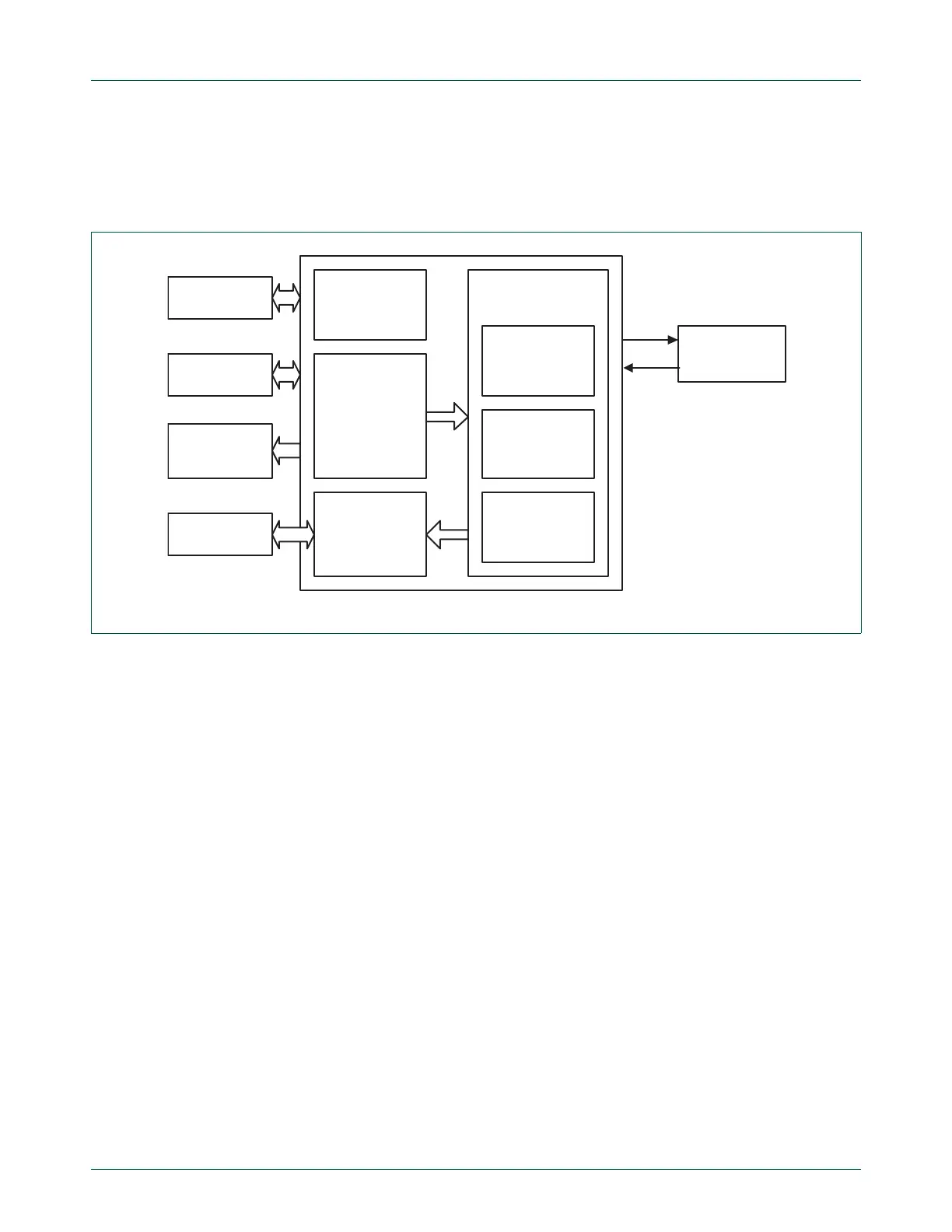

Chapter 16: LPC176x/5x CAN1/2

• Nested Vectored Interrupt Controller (NVIC)

• CAN Transceiver

• Common Status Registers

16.5.1 APB Interface Block (AIB)

The APB Interface Block provides access to all CAN Controller registers.

16.5.2 Interface Management Logic (IML)

The Interface Management Logic interprets commands from the CPU, controls internal

addressing of the CAN Registers and provides interrupts and status information to the

CPU.

16.5.3 Transmit Buffers (TXB)

The TXB represents a Triple Transmit Buffer, which is the interface between the Interface

Management Logic (IML) and the Bit Stream Processor (BSP). Each Transmit Buffer is

able to store a complete message which can be transmitted over the CAN network. This

buffer is written by the CPU and read out by the BSP.

Fig 53. CAN controller block diagram

INTERFACE

MANAGEMENT

LOGIC

TRANSMIT

BUFFERS 1,2

AND 3

RECEIVE

BUFFERS 1

AND 2

BIT

TIMING

LOGIC

BIT

STREAM

PROCESSOR

ERROR

MANAGEMENT

LOGIC

CAN CORE

BLOCK

NVIC

APB BUS

ACCEPTANCE

FILTER

COMMON

STATUS

REGISTER

CAN

TRANSCEIVER

TX

RX

Loading...

Loading...