UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 49 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

4.6.2 PLL1 Control register (PLL1CON - 0x400F C0A0)

The PLL1CON register contains the bits that enable and connect PLL1. Enabling PLL1

allows it to attempt to lock to the current settings of the multiplier and divider values.

Connecting PLL1 causes the USB subsystem to run from the PLL1 output clock. Changes

to the PLL1CON register do not take effect until a correct PLL feed sequence has been

given (see Section 4.6.6

and Section 4.6.3).

PLL1CFG PLL1 Configuration Register. Holding register

for updating PLL1 configuration values. Values

written to this register do not take effect until a

valid PLL1 feed sequence has taken place.

R/W 0 0x400F C0A4

PLL1STAT PLL1 Status Register. Read-back register for

PLL1 control and configuration information. If

PLL1CON or PLL1CFG have been written to,

but a PLL1 feed sequence has not yet occurred,

they will not reflect the current PLL1 state.

Reading this register provides the actual values

controlling PLL1, as well as PLL1 status.

RO 0 0x400F C0A8

PLL1FEED PLL1 Feed Register. This register enables

loading of PLL1 control and configuration

information from the PLL1CON and PLL1CFG

registers into the shadow registers that actually

affect PLL1 operation.

WO NA 0x400F C0AC

Table 29. PLL1 registers

Name Description Access Reset

value

[1]

Address

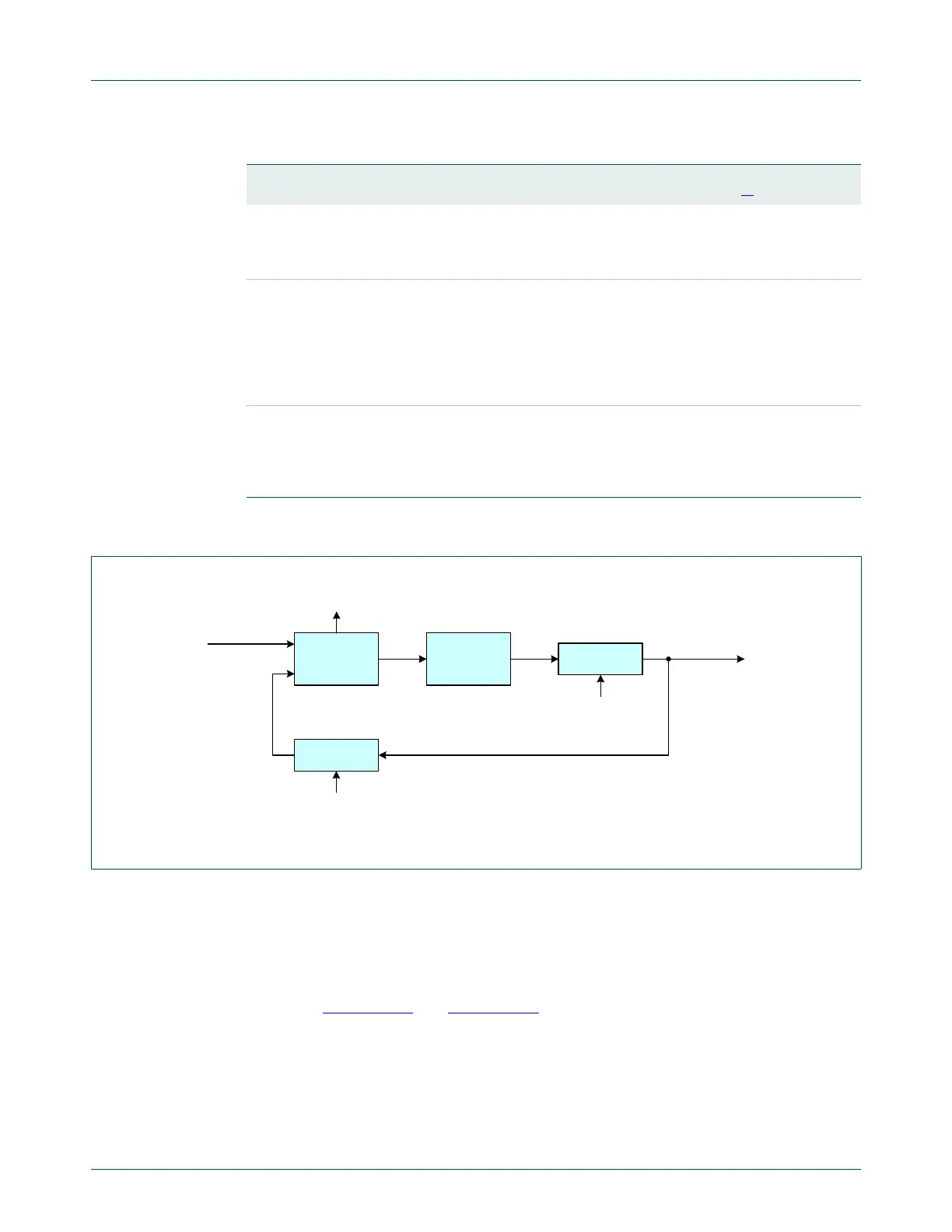

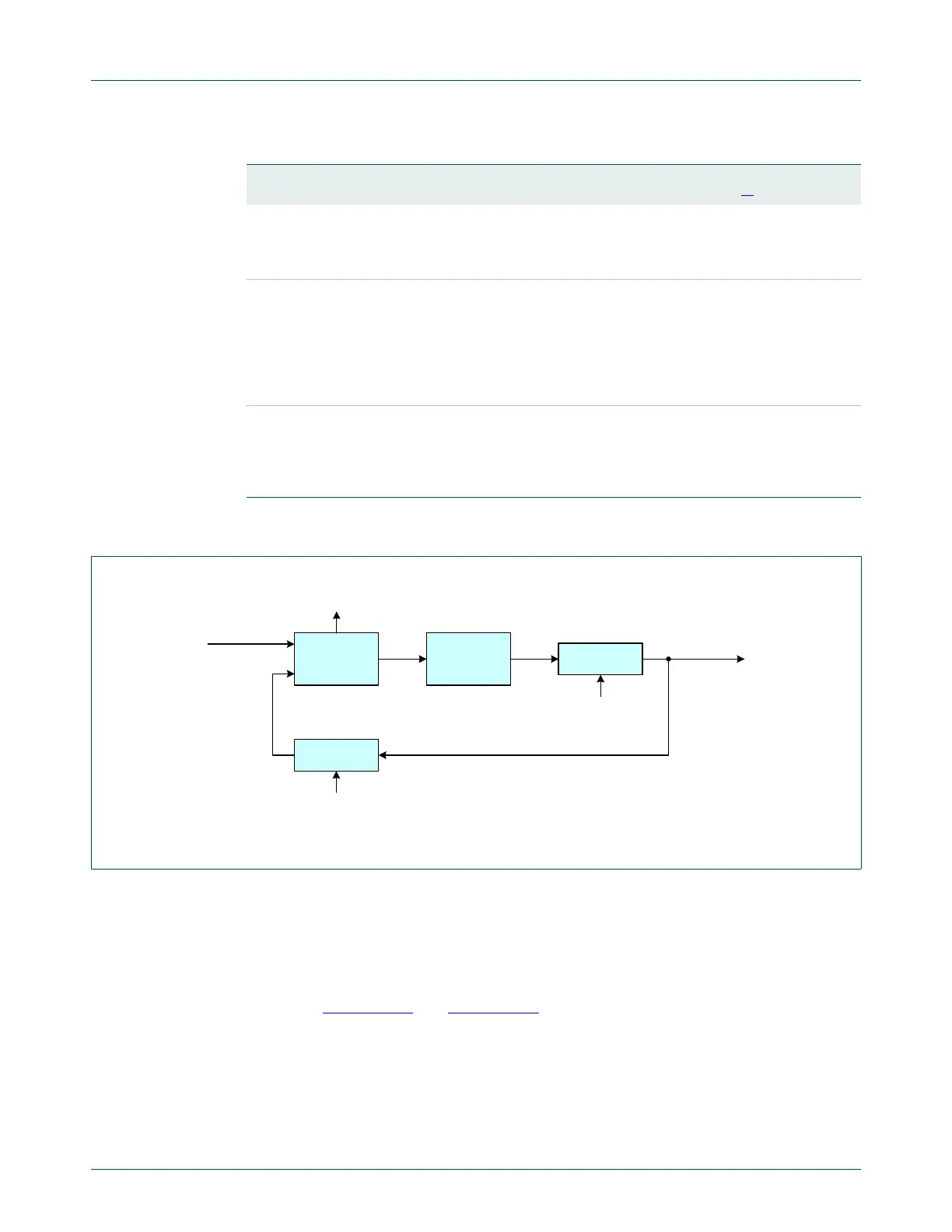

Fig 10. PLL1 block diagram

100416

PLL output

clock

Divide by 2P

Phase

Detector

PLOCK

PLLSTAT[10]

Current-

Controlled

Oscillator

Fcco

PSEL

PLLSTAT[6:5]

PLL input

clock

Divide by M

MSEL

PLLSTAT[4:0]

Loading...

Loading...