UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 594 of 841

NXP Semiconductors

UM10360

Chapter 31: LPC176x/5x General Purpose DMA (GPDMA)

31.5 Register description

The DMA Controller supports 8 channels. Each channel has registers specific to the

operation of that channel. Other registers controls aspects of how source peripherals

relate to the DMA Controller. There are also global DMA control and status registers.

The DMA Controller registers are shown in Table 544

.

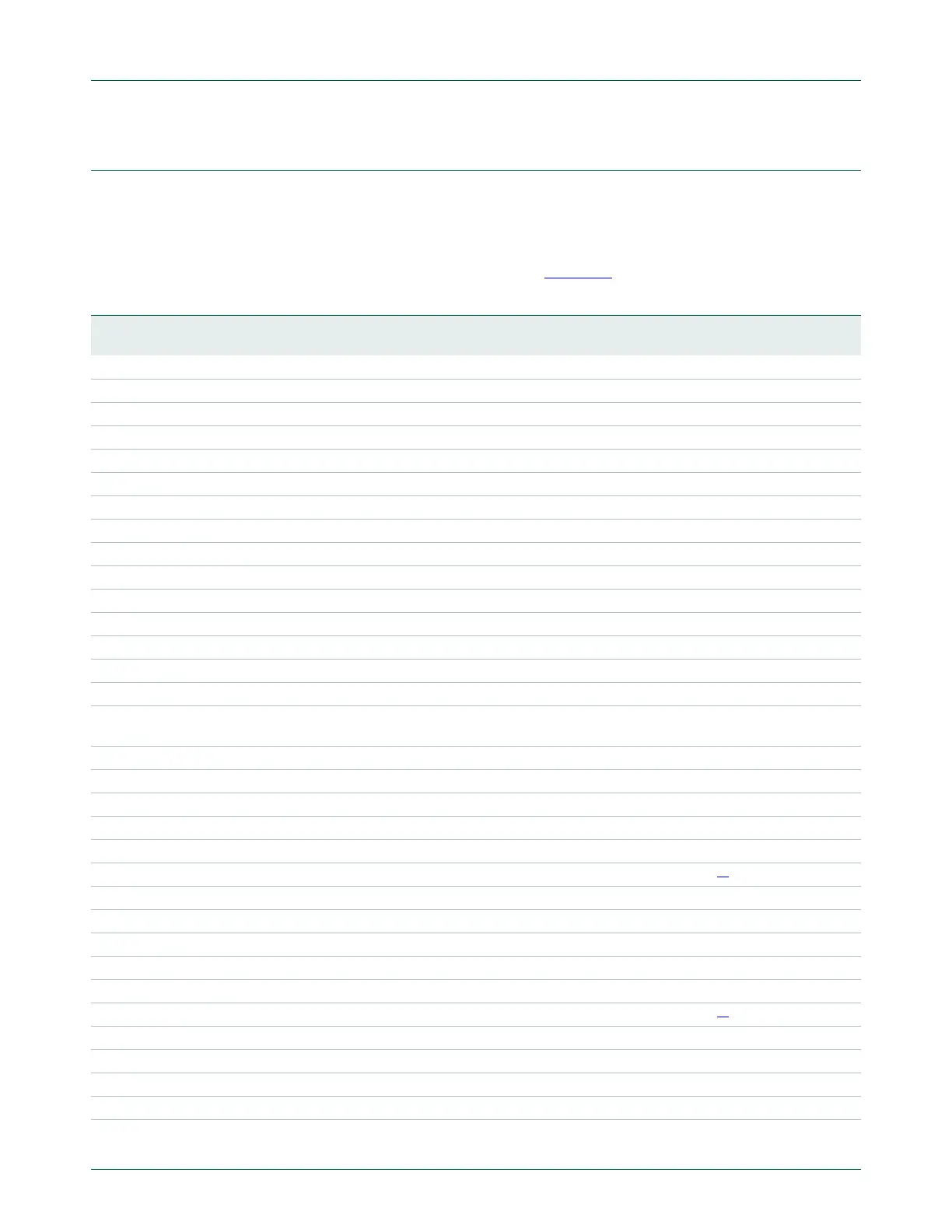

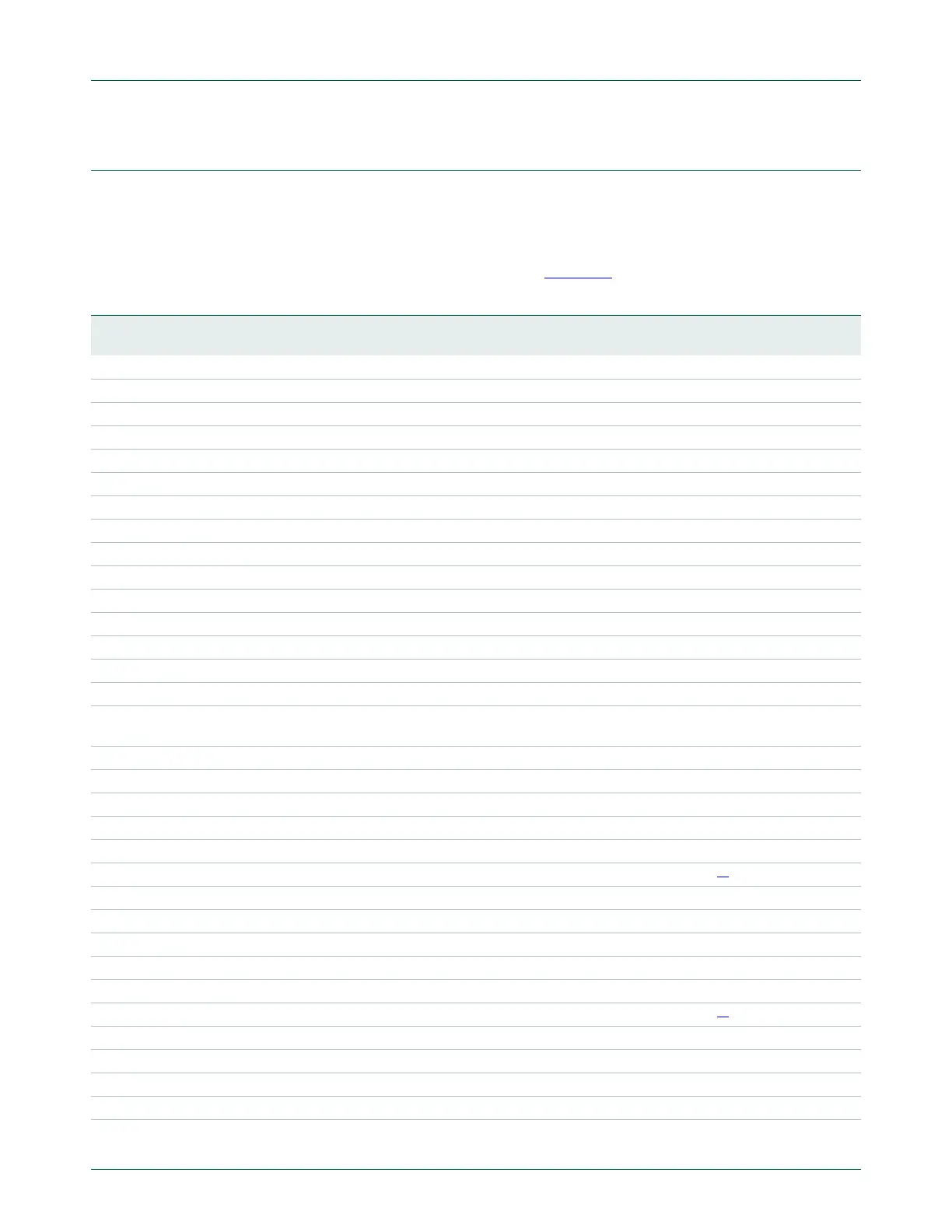

Table 544. GPDMA register map

Name Description Access Reset

state

Address

General registers

DMACIntStat DMA Interrupt Status Register RO 0 0x5000 4000

DMACIntTCStat DMA Interrupt Terminal Count Request Status Register RO 0 0x5000 4004

DMACIntTCClear DMA Interrupt Terminal Count Request Clear Register WO - 0x5000 4008

DMACIntErrStat DMA Interrupt Error Status Register RO 0 0x5000 400C

DMACIntErrClr DMA Interrupt Error Clear Register WO - 0x5000 4010

DMACRawIntTCStat DMA Raw Interrupt Terminal Count Status Register RO 0 0x5000 4014

DMACRawIntErrStat DMA Raw Error Interrupt Status Register RO 0 0x5000 4018

DMACEnbldChns DMA Enabled Channel Register RO 0 0x5000 401C

DMACSoftBReq DMA Software Burst Request Register R/W 0 0x5000 4020

DMACSoftSReq DMA Software Single Request Register R/W 0 0x5000 4024

DMACSoftLBReq DMA Software Last Burst Request Register R/W 0 0x5000 4028

DMACSoftLSReq DMA Software Last Single Request Register R/W 0 0x5000 402C

DMACConfig DMA Configuration Register R/W 0 0x5000 4030

DMACSync DMA Synchronization Register R/W 0 0x5000 4034

DMAREQSEL Selects between UART and timer DMA requests on

channels 8 through 15

R/W 0 0x400F C1C4

Channel 0 registers

DMACC0SrcAddr DMA Channel 0 Source Address Register R/W 0 0x5000 4100

DMACC0DestAddr DMA Channel 0 Destination Address Register R/W 0 0x5000 4104

DMACC0LLI DMA Channel 0 Linked List Item Register R/W 0 0x5000 4108

DMACC0Control DMA Channel 0 Control Register R/W 0 0x5000 410C

DMACC0Config DMA Channel 0 Configuration Register R/W 0

[1]

0x5000 4110

Channel 1 registers

DMACC1SrcAddr DMA Channel 1 Source Address Register R/W 0 0x5000 4120

DMACC1DestAddr DMA Channel 1 Destination Address Register R/W 0 0x5000 4124

DMACC1LLI DMA Channel 1 Linked List Item Register R/W 0 0x5000 4128

DMACC1Control DMA Channel 1 Control Register R/W 0 0x5000 412C

DMACC1Config DMA Channel 1 Configuration Register R/W 0

[1]

0x5000 4130

Channel 2 registers

DMACC2SrcAddr DMA Channel 2 Source Address Register R/W 0 0x5000 4140

DMACC2DestAddr DMA Channel 2 Destination Address Register R/W 0 0x5000 4144

DMACC2LLI DMA Channel 2 Linked List Item Register R/W 0 0x5000 4148

DMACC2Control DMA Channel 2 Control Register R/W 0 0x5000 414C

Loading...

Loading...