UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 53 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

4.6.8 PLL1 frequency calculation

The PLL1 equations use the following parameters:

The PLL1 output frequency (when the PLL is both active and connected) is given by:

USBCLK = M F

OSC

or USBCLK = F

CCO

/ (2 P)

The CCO frequency can be computed as:

F

CCO

= USBCLK 2 P or F

CCO

= F

OSC

M 2 P

The PLL1 inputs and settings must meet the following criteria:

• F

OSC

is in the range of 10 MHz to 25 MHz.

• USBCLK is 48 MHz.

• F

CCO

is in the range of 156 MHz to 320 MHz.

4.6.9 Procedure for determining PLL1 settings

The PLL1 configuration for USB may be determined as follows:

1. The desired PLL1 output frequency is USBCLK = 48 MHz.

2. Choose an oscillator frequency (F

OSC

). USBCLK must be the whole (non-fractional)

multiple of F

OSC

meaning that the possible values for F

OSC

are 12 MHz, 16 MHz, and

24 MHz.

3. Calculate the value of M to configure the MSEL1 bits. M = USBCLK / F

OSC

. In this

case, the possible values for M = 2, 3, or 4 (F

OSC

= 24 MHz, 16 MHz, or 12 MHz). The

value written to the MSEL1 bits in PLL1CFG is M 1 (see Table 37

).

4. Find a value for P to configure the PSEL1 bits, such that F

CCO

is within its defined

frequency limits of 156 MHz to 320 MHz. F

CCO

is calculated using F

CCO

= USBCLK

2 P. It follows that P = 2 is the only P value to yield F

CCO

in the allowed range. The

value written to the PSEL1 bits in PLL1CFG is ‘01’ for P = 2 (see Table 36

).

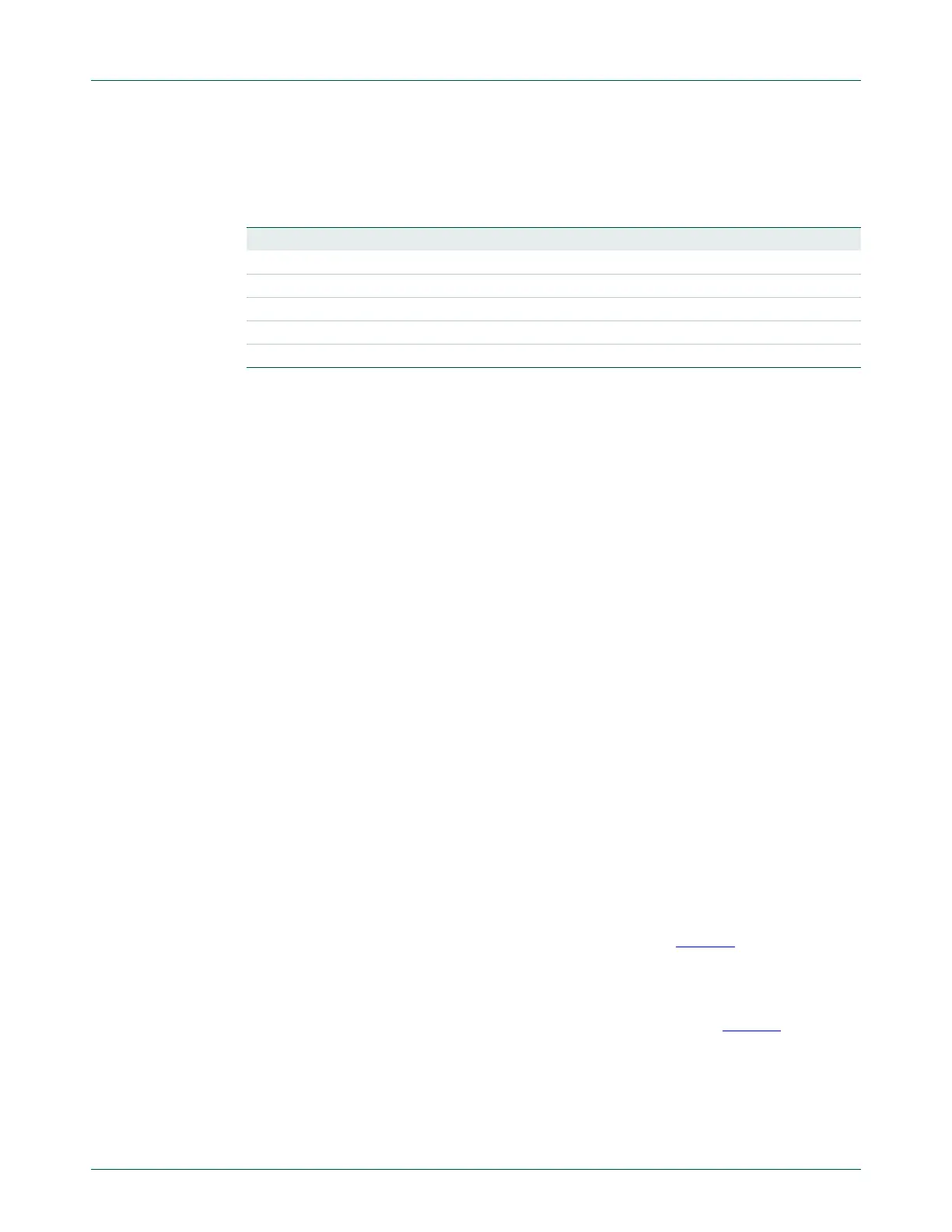

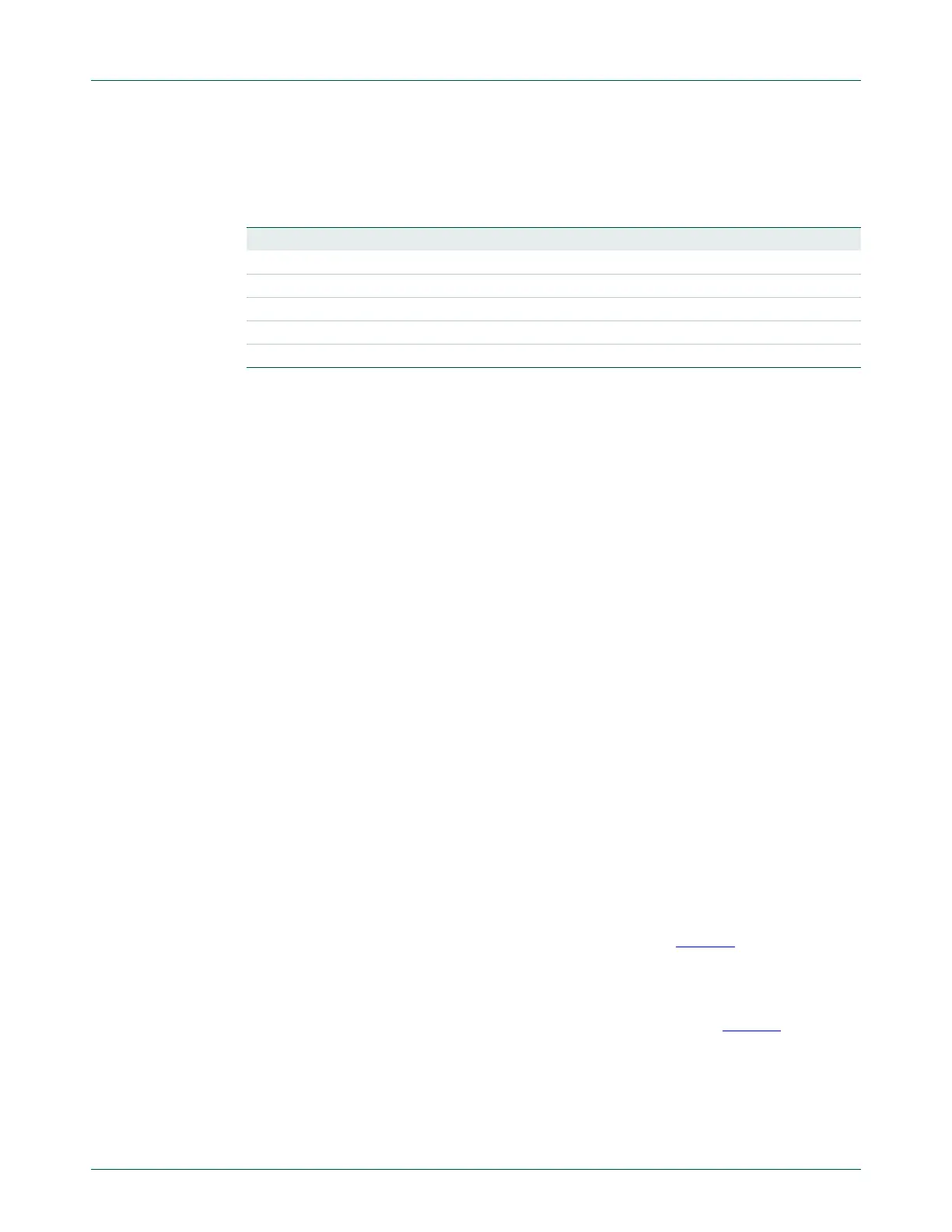

Table 35. Elements determining PLL frequency

Element Description

F

OSC

the frequency from the crystal oscillator

F

CCO

the frequency of the PLL1 current controlled oscillator

USBCLK the PLL1 output frequency (48 MHz for USB)

M PLL1 Multiplier value from the MSEL1 bits in the PLL1CFG register

P PLL1 Divider value from the PSEL1 bits in the PLL1CFG register

Loading...

Loading...