UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 522 of 841

NXP Semiconductors

UM10360

Chapter 24: LPC176x/5x Pulse Width Modulator (PWM)

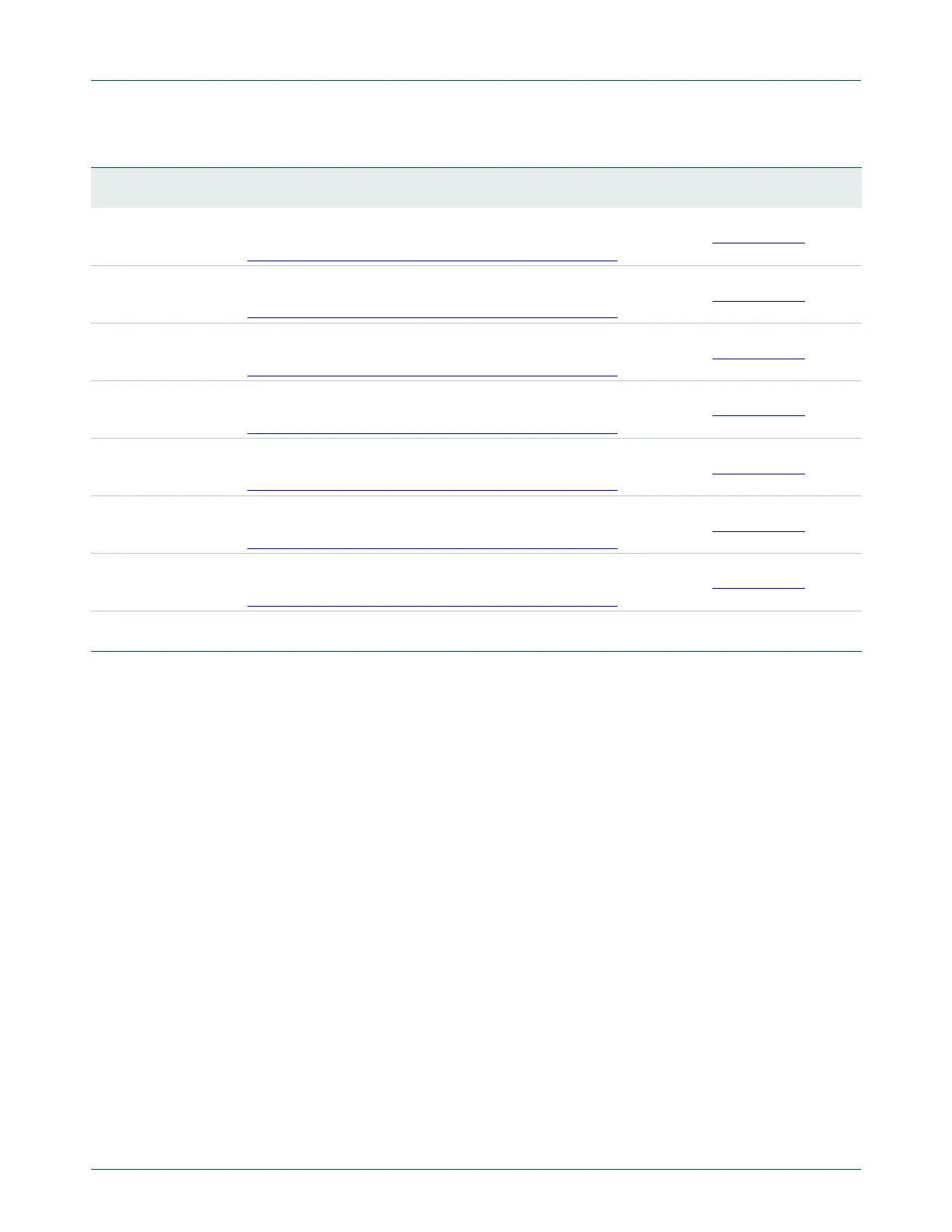

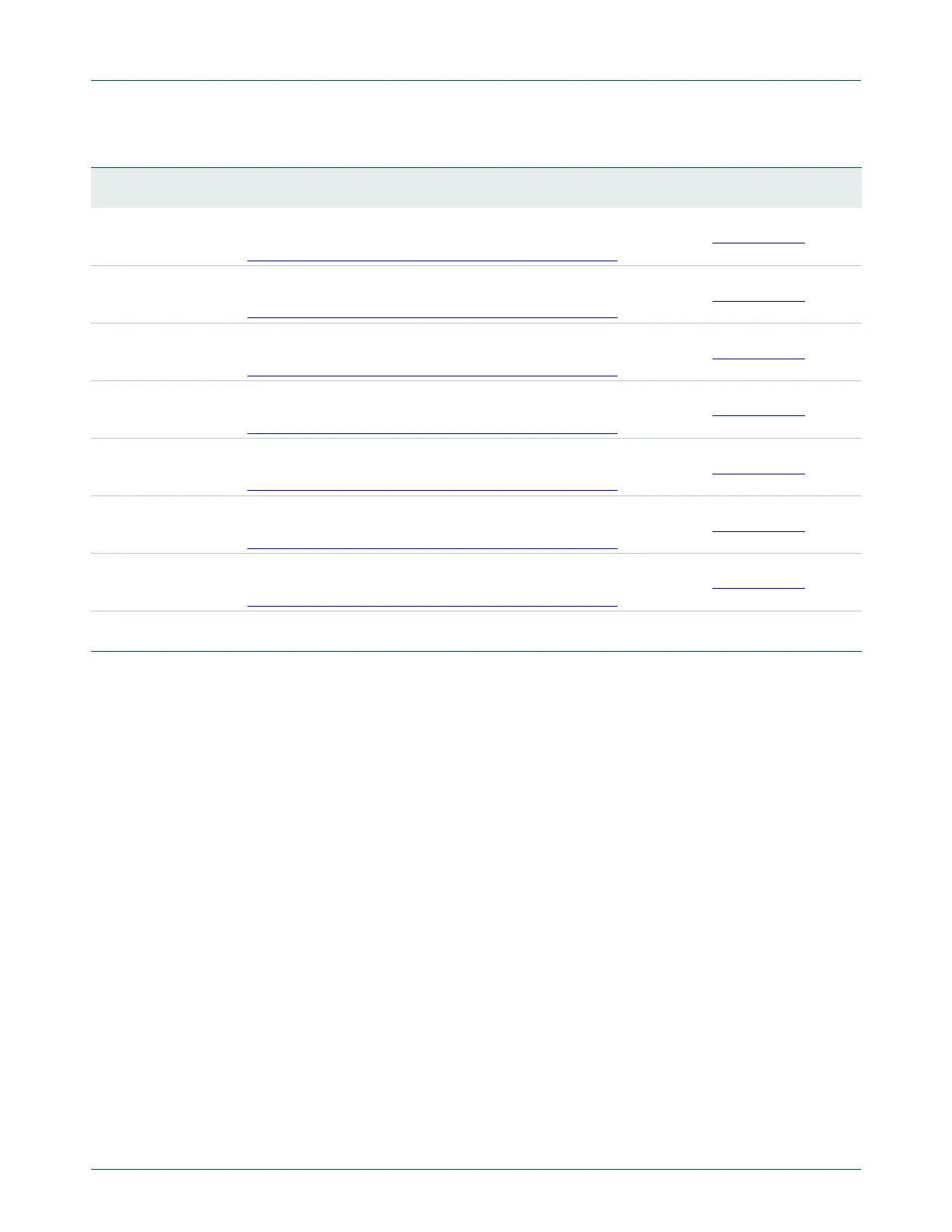

Table 452: PWM Latch Enable Register (PWM1LER - address 0x4001 8050) bit description

Bit Symbol Description Reset

Value

0 Enable PWM

Match 0 Latch

Writing a one to this bit allows the last value written to the PWM Match 0 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

1 Enable PWM

Match 1 Latch

Writing a one to this bit allows the last value written to the PWM Match 1 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

2 Enable PWM

Match 2 Latch

Writing a one to this bit allows the last value written to the PWM Match 2 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

3 Enable PWM

Match 3 Latch

Writing a one to this bit allows the last value written to the PWM Match 3 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

4 Enable PWM

Match 4 Latch

Writing a one to this bit allows the last value written to the PWM Match 4 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

5 Enable PWM

Match 5 Latch

Writing a one to this bit allows the last value written to the PWM Match 5 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

6 Enable PWM

Match 6 Latch

Writing a one to this bit allows the last value written to the PWM Match 6 register to be

become effective when the timer is next reset by a PWM Match event. See Section 24.6.4

“PWM Match Control Register (PWM1MCR - 0x4001 8014)”.

0

31:7 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...