Embedded Flash memory (FLASH) RM0453

144/1454 RM0453 Rev 2

4.10.16 FLASH CPU2 access control register (FLASH_C2ACR)

Address offset: 0x05C

Reset value: 0x0000 0600

4.10.17 FLASH CPU2 status register (FLASH_C2SR)

Address offset: 0x060

Reset value: 0x0000 0000

Access: no wait state. Word, half-word and byte access.

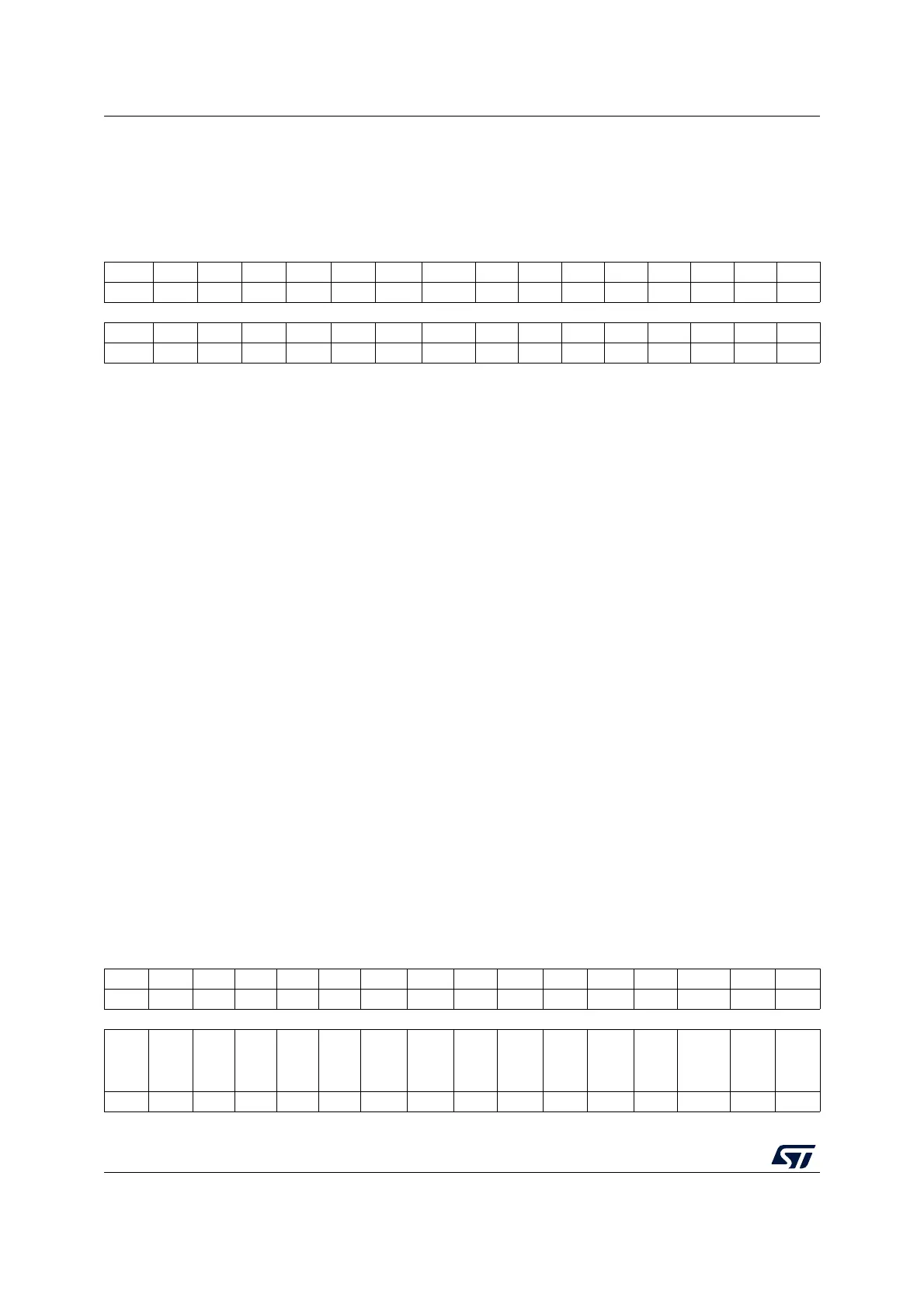

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PES Res. Res. Res. ICRST Res. ICEN PRFTEN Res. Res. Res. Res. Res. Res. Res. Res.

rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 PES: CPU2 program/erase suspend request

0: Flash program and erase operations granted

1: Any new Flash program and erase operation is suspended until this bit and the same bit

in FLASH_ACR are cleared. The PESD bit in FLASH_SR and FLASH_C2SR are set when

at least one PES bit in FLASH_ACR or FLASH_C2ACR is set.

Bits 14:12 Reserved, must be kept at reset value.

Bit 11 ICRST: CPU2 instruction cache reset

0: CPU2 instruction cache not reset

1: CPU2 instruction cache reset

This bit can be written only when the instruction cache is disabled.

Bit 10 Reserved, must be kept at reset value.

Bit 9 ICEN: CPU2 instruction cache enable

0: CPU2 instruction cache disabled

1: CPU2 instruction cache enabled

Bit 8 PRFTEN: CPU2 prefetch enable.

0: CPU2 prefetch disabled

1: CPU2 prefetch enabled.

Bits 7:0 Reserved, must be kept at reset value.

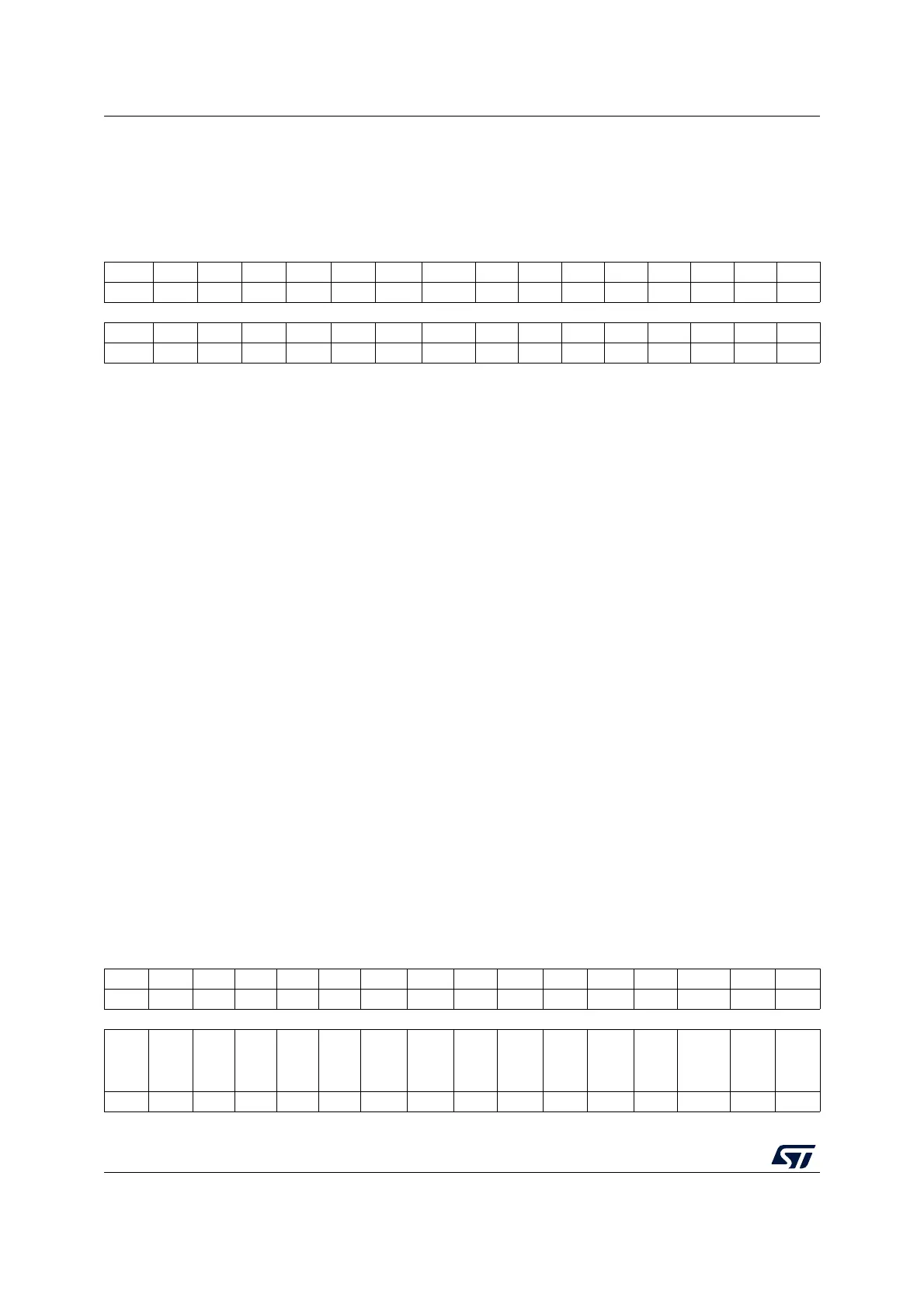

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. PESD CFGBSY Res. BSY

rr r

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res.

RDERR

Res. Res. Res. Res.

FASTERR

MISSERR

PGSERR

SIZERR

PGAERR

WRPERR

PROGERR

Res.

OPERR

EOP

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Loading...

Loading...