Sub-GHz radio (SUBGHZ) RM0453

186/1454 RM0453 Rev 2

The correct values selected in the table below must be carefully tested to ensure a good

detection at sensitivity level and to limit the number of false detections.

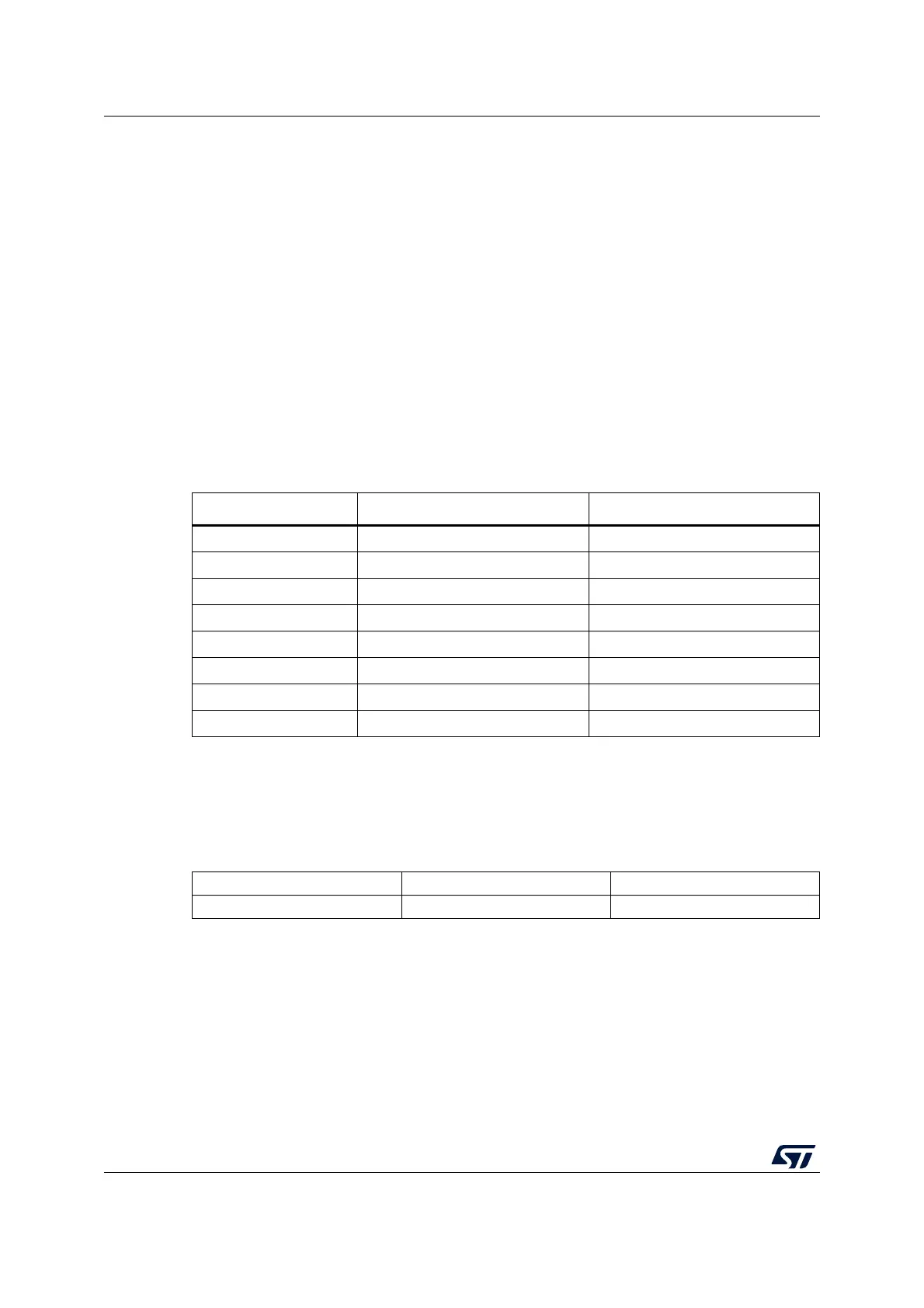

Set_BufferBaseAddress() command

Set_BufferBaseAddress(TxBaseAddr, RxBaseAddr) sets the data buffer base

address for the packet handling in TX and RX.

byte 4 bits 7:1 Reserved, must be kept at reset value.

Bit 0 CadExitMode: defines the sub-GHz radio operating mode to enter after CAD

scan is finished

0: Standby with RC 13 MHz mode entry after CAD, whatever is detected

during the CAD scan

1: Standby with RC 13 MHz mode after CAD if no LoRa symbol is detected

during the CAD scan

if a LoRa symbol is detected, the sub-GHz radio stays in Receive mode until a

packet is received or until the CAD timeout is reached.

bytes 7:5 bits 23:0 Timeout[23:0]: CAD timeout = Timeout[23:0] x 15.625 μs

The CAD timeout is only used when a symbol is detected and

CadExitMode = 1 (stay in Receive mode after a LoRa symbol detection).

0x000000 - 0xFFFFFF: timeout, resolution 15.625 μs

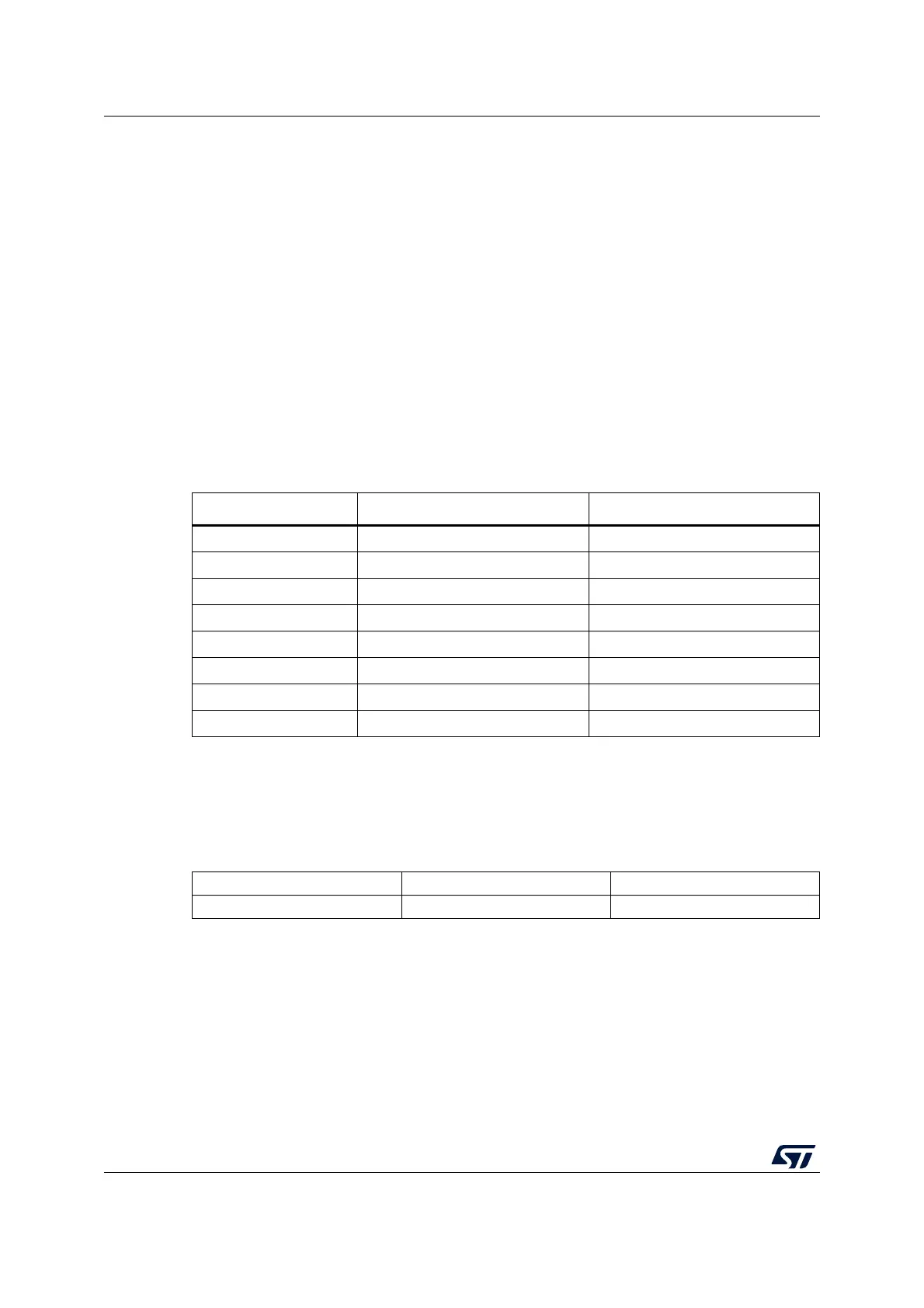

Table 36. Recommended CAD configuration settings

SF CadDetPeak[7:0] CadDetMin[7:0]

5 0x18 0x10

6 0x19 0x10

7 0x20 0x10

8 0x21 0x10

9 0x22 0x10

10 0x23 0x10

11 0x24 0x10

12 0x25 0x10

012

Opcode TxBaseAddr[7:0] RxBaseAddr[7:0]

www

byte 0 bits 7:0 Opcode: 0x8F

byte 1 bits 7:0 TxBaseAddr[7:0]: Tx base address offset relative to the sub-GHz RAM base

address

byte 2 bits 7:0 RxBaseAddr[7:0]: Rx base address offset relative to the sub-GHz RAM base

address

Loading...

Loading...