RM0453 Rev 2 93/1454

RM0453 Global security controller (GTZC)

96

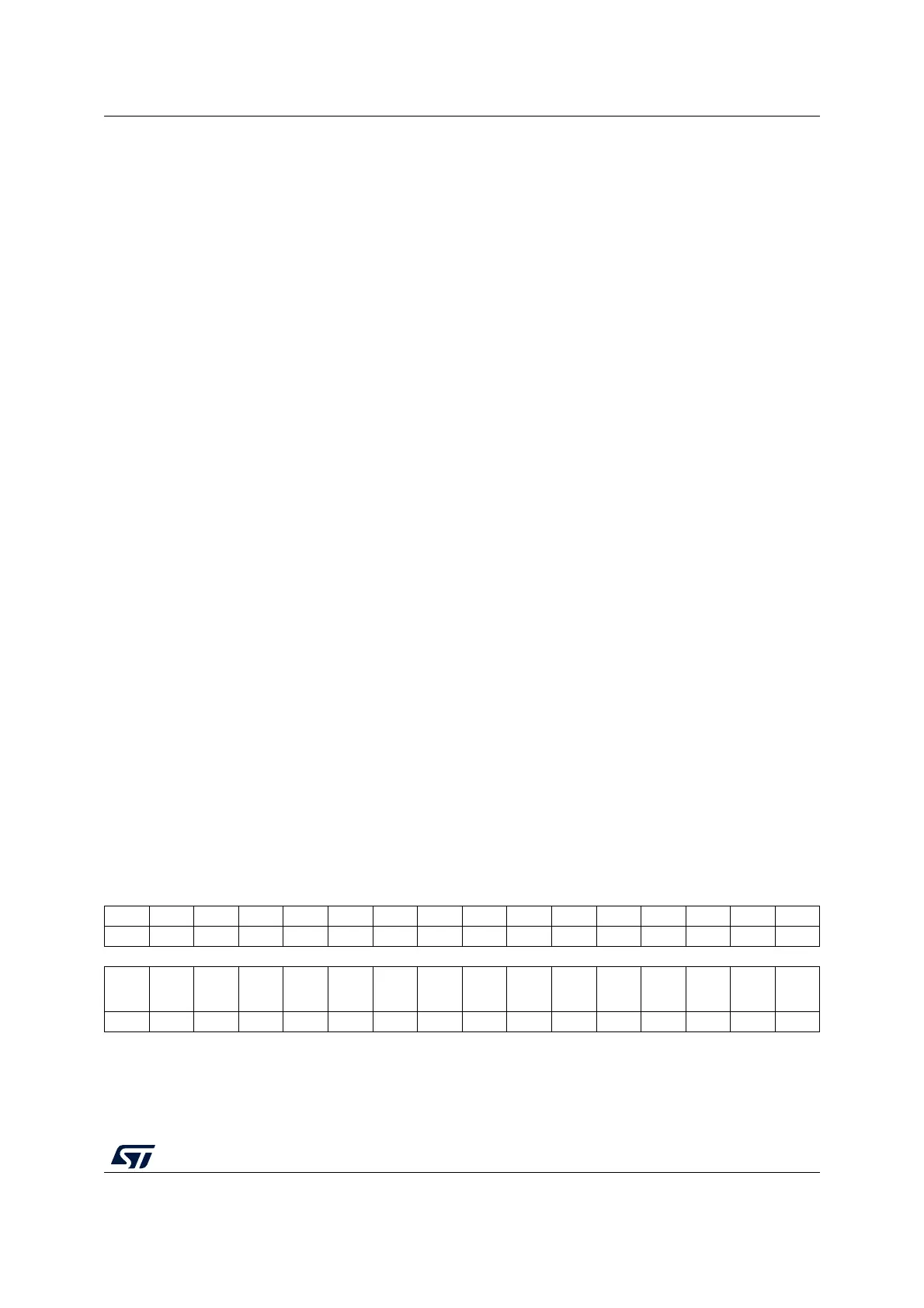

3.6.2 GTZC TZIC status register 1 (GTZC_TZIC_MISR1)

Address offset: 0x010

Reset value: 0x0000 0000

This register can only be access by a secure privileged access for read and write. A non

secure or unprivileged access is ignored and return zero data and an illegal access event is

generated.

Note: When the system is non-secure (ESE = 0) this register cannot be written and reads zero.

Bit 7 DMA1IE: Illegal access event interrupt enable bit for DMA1

0: Disabled (masked)

1: Enabled (unmasked)

Bit 6 FLASHIFIE: Illegal access event interrupt enable bit for FLASH interface

0: Disabled (masked)

1: Enabled (unmasked)

Bit 5 PWRIE: Illegal access event interrupt enable bit for PWR

0: Disabled (masked)

1: Enabled (unmasked)

Bit 4 SUBGHZSPIIE: Illegal access event interrupt enable bit for sub-GHz SPI

0: Disabled (masked)

1: Enabled (unmasked)

Bit 3 RNGIE: Illegal access event interrupt enable bit for RNG

0: Disabled (masked)

1: Enabled (unmasked)

Bit 2 AESIE: Illegal access event interrupt enable bit for AES

0: Disabled (masked)

1: Enabled (unmasked)

Bit 1 TZSCIE: Illegal access event interrupt enable bit for GTZC TZSC

0: Disabled (masked)

1: Enabled (unmasked)

Bit 0 TZICIE: Illegal access event interrupt enable bit for GTZC TZIC

0: Disabled (masked)

1: Enabled (unmasked)

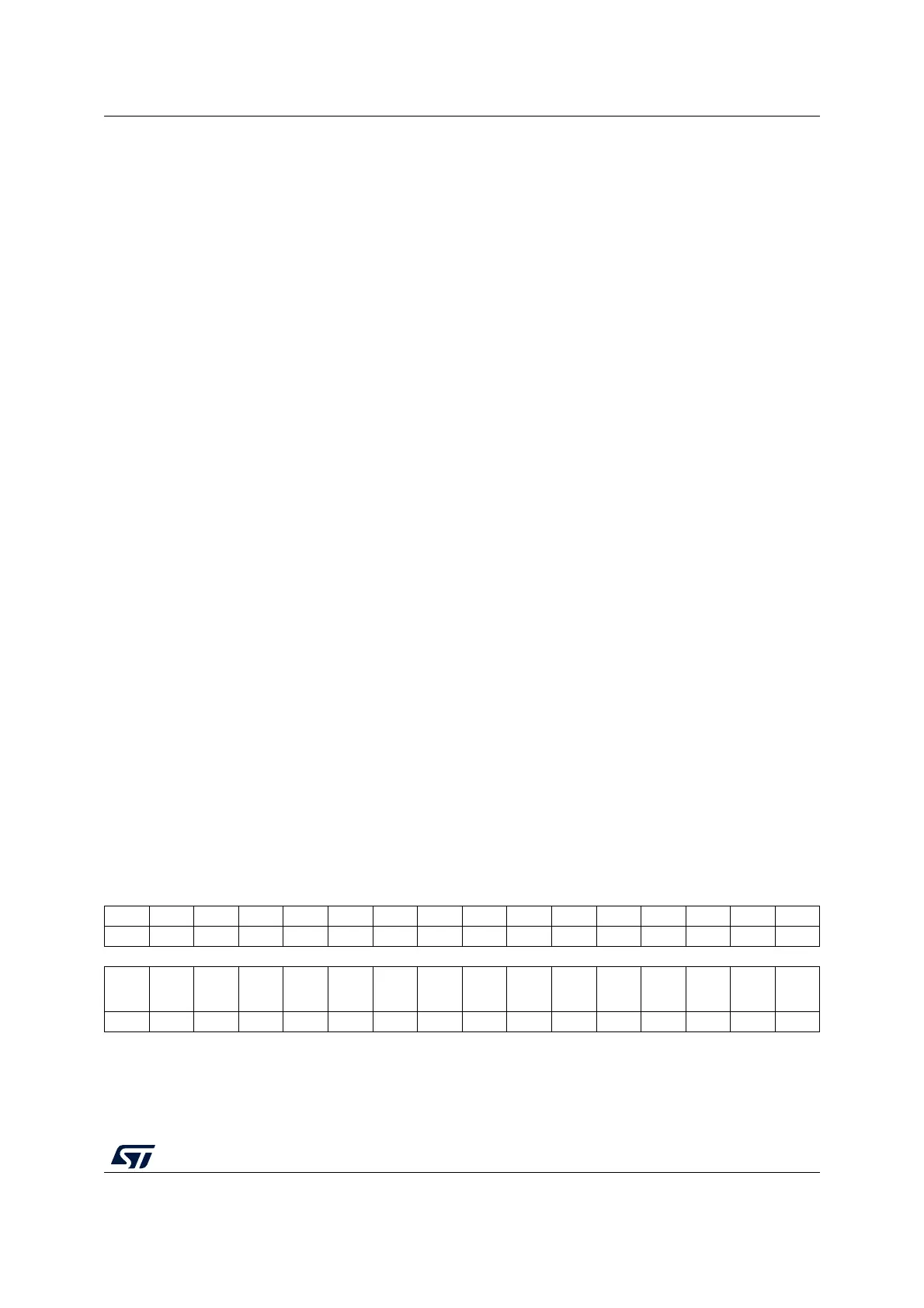

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. PKAMF

SRAM2

MF

SRAM1

MF

FLASH

MF

DMAM

UX1MF

DMA2

MF

DMA1

MF

FLASHI

FMF

PWR

MF

SUBG

HZSPI

MF

RNG

MF

AESMF

TZSC

MF

TZIC

MF

rrrrrrrrrrrrrr

Bits 31:14 Reserved, must be kept at reset value.

Loading...

Loading...