Power control (PWR) RM0453

236/1454 RM0453 Rev 2

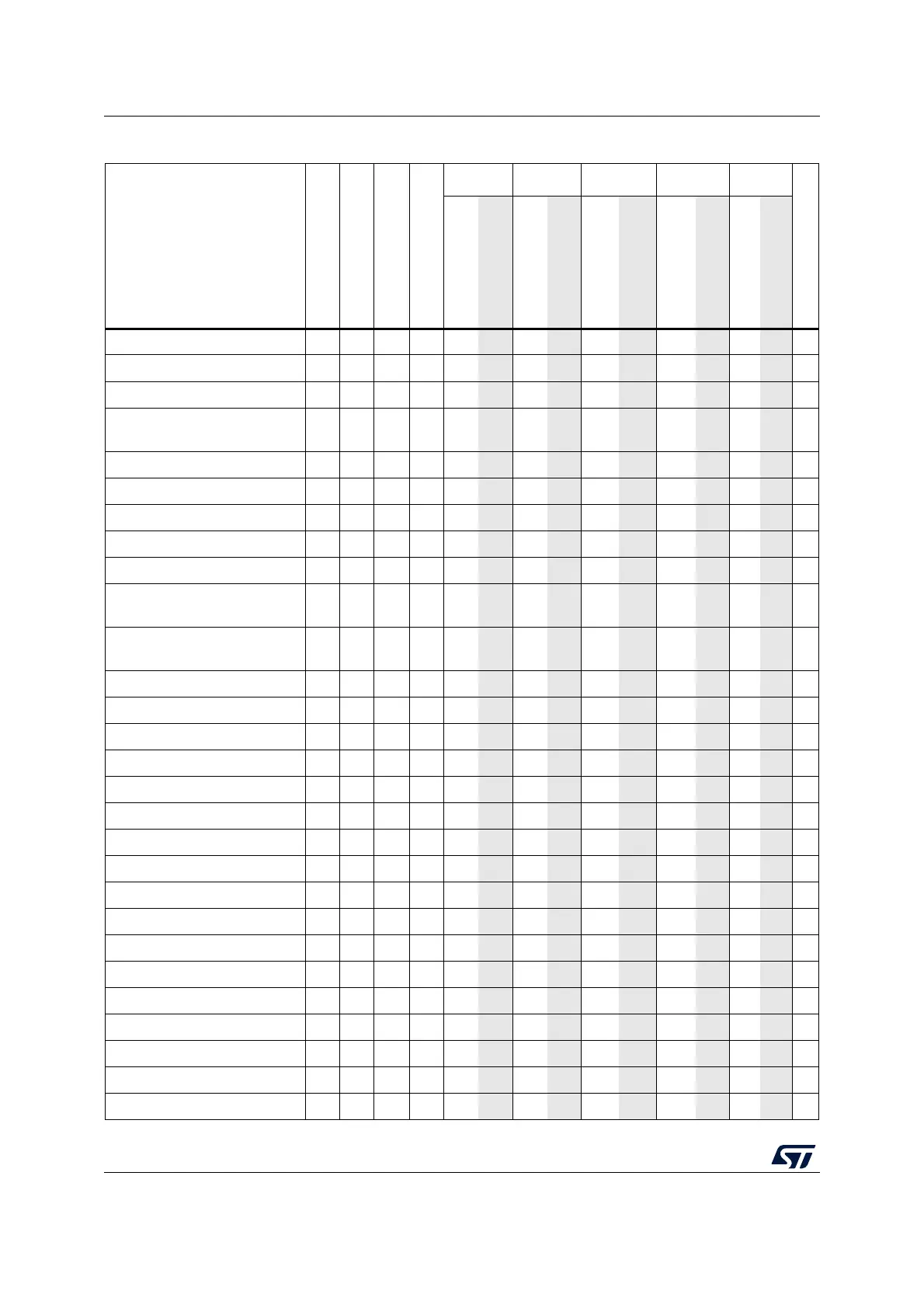

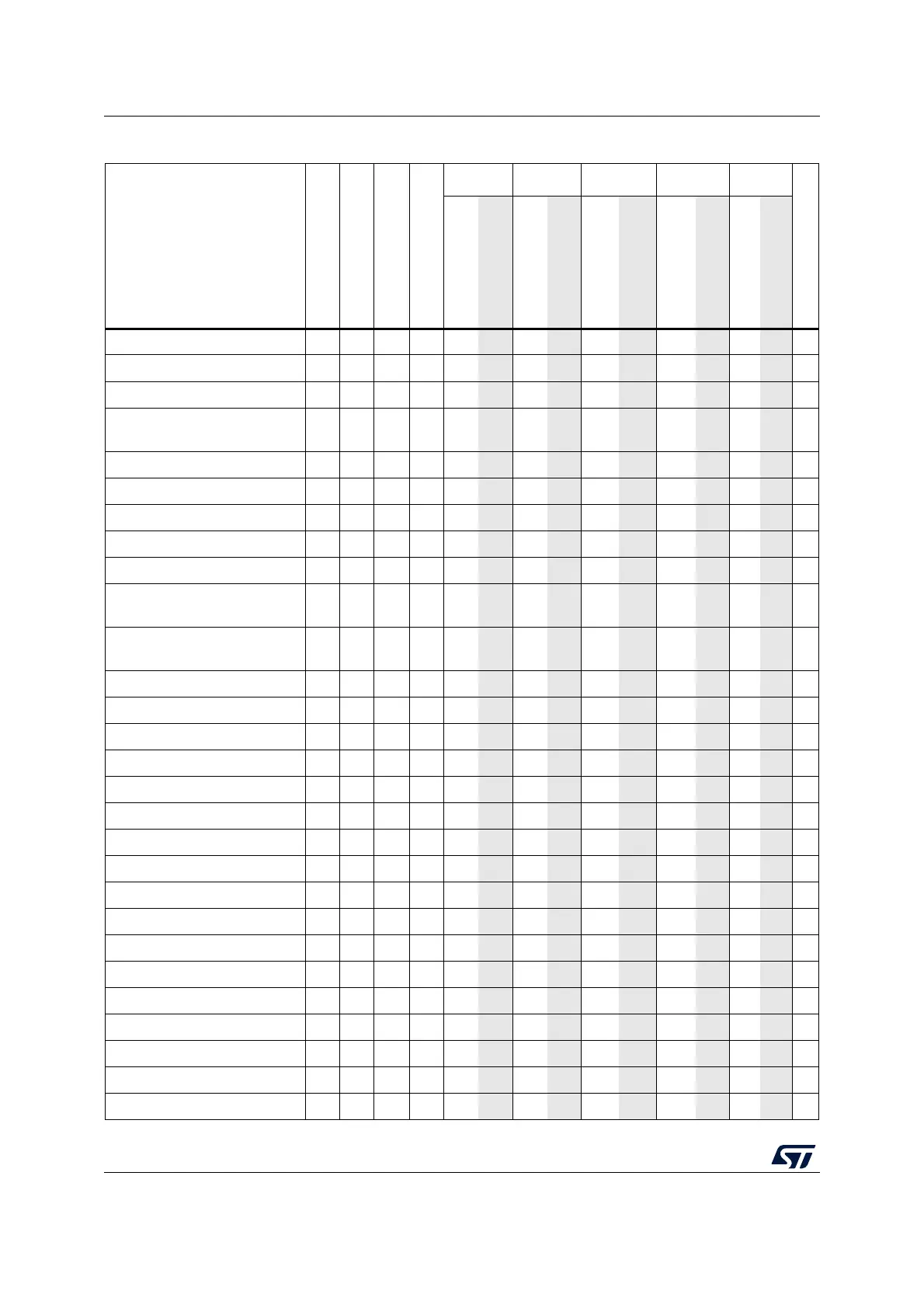

Table 45. Functionalities depending on system operating mode

(1)

Peripheral

Run

Sleep

LPRun

LPSleep

Stop 0 Stop 1 Stop 2 Standby Shutdo

VBAT

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

CPU1 Y - Y - R -R-R ------

CPU2 Y - Y - R

-R-R------

Radio-system (sub-GHz) O O O O O

OOOOOOO---

Flash memory

(up to 256 Kbytes)

YO

(2)

O

(3)

O

(2)

(3)

R -R-R-R-R-R

Flash memory interface Y Y Y Y R -R-R ------

SRAM1 Y O

(2)

YO

(2)

R -R-R------

SRAM2 Y O

(2)

YO

(2)

R -R-R-O

(4)

----

Backup registers Y Y Y Y R

-R-R-R-R-R

Brownout reset (BOR) Y Y Y Y Y

YYYYYYY---

Programmable voltage

detector (PVD)

OOOOOOOOOOO

(5)

O

(5)

- --

Peripheral voltage monitor

(PVM3)

OOOOO

OOOOO-----

DMAx (x = 1, 2) O O O O R -R-- ------

DMAMUX1 O O O O R

-R--------

High-speed internal (HSI16) O O O O O

(6)

-O

(6)

-O

(6)

------

High-speed external (HSE32) O O O

(7)

O

(7)

O

(7)

-O

(7)

-O

(7)

-O

(7)

----

Low-speed internal (LSI) O O O O O

-O-O-O----

Low-speed external (LSE) O O O O O

-O-O-O-O-O

Multi-speed internal (MSI) O O O O O

-O-O------

Clock security system (CSS) O O O O R

-R--------

Clock security system on LSE O O O O O

OOOOOOO---

RTC/auto wakeup O O O O O

OOOOOOOOOO

Number of TAMP tamper pins 3 3 3 3 3

O3O3O3O3O3

USARTx (x= 1, 2) O O O O O

(8)

O

(8)

O

(8)

O

(8)

- ------

Low-power UART (LPUART1) O O O O O

(8)

O

(8)

O

(8)

O

(8)

O

(8)

O

(8)

- ----

I2Cx (x = 1, 2) O O O O O

(9)

O

(9)

O

(9)

O

(9)

- ------

I2C3 O O O O O

(9)

O

(9)

O

(9)

O

(9)

O

(9)

O

(9)

- ----

SPI1 O O O O R

-R--------

SUBGHZSPI O O O O R

-R--------

Loading...

Loading...