Hardware semaphore (HSEM) RM0453

374/1454 RM0453 Rev 2

8.4.6 HSEM interrupt status register (HSEM_CnMISR)

Address offset: 0x10C + 0x010 * (n - 1), (n = 1 to 2)

Reset value: 0x0000 0000

8.4.7 HSEM clear register (HSEM_CR)

Address offset: 0x140

Reset value: 0x0000 0000

Only write accesses with authorized AHB bus master IDs are granted. Write accesses with

unauthorized AHB bus master IDs are discarded.

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 ISF[15:0]: Interrupt semaphore x status bit before enable (mask) (x = 0 to 15)

This bit is set by hardware, and reset only by software. This bit is cleared by software writing

the corresponding HSEM_CnICR bit.

0: Interrupt semaphore x status, no interrupt pending

1: Interrupt semaphore x status, interrupt pending

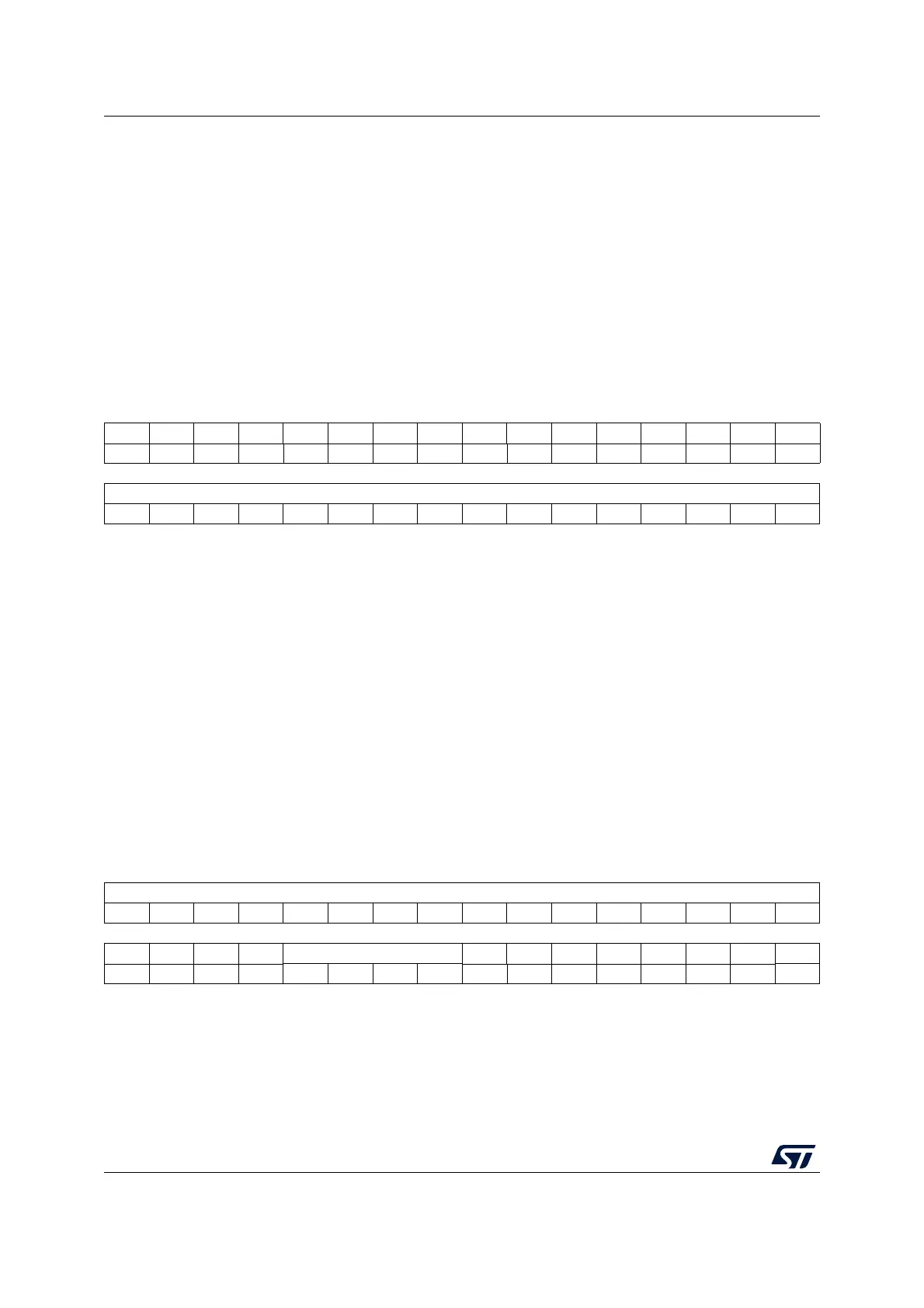

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

MISF[15:0]

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 MISF[15:0]: Masked interrupt(n) semaphore x status bit after enable (mask) (x = 0 to 15)

This bit is set by hardware and read only by software. This bit is cleared by software writing

the corresponding HSEM_CnICR bit. This bit is read as 0 when semaphore x status is

masked in HSEM_CnIER bit x.

0: interrupt(n) semaphore x status after masking not pending

1: interrupt(n) semaphore x status after masking pending

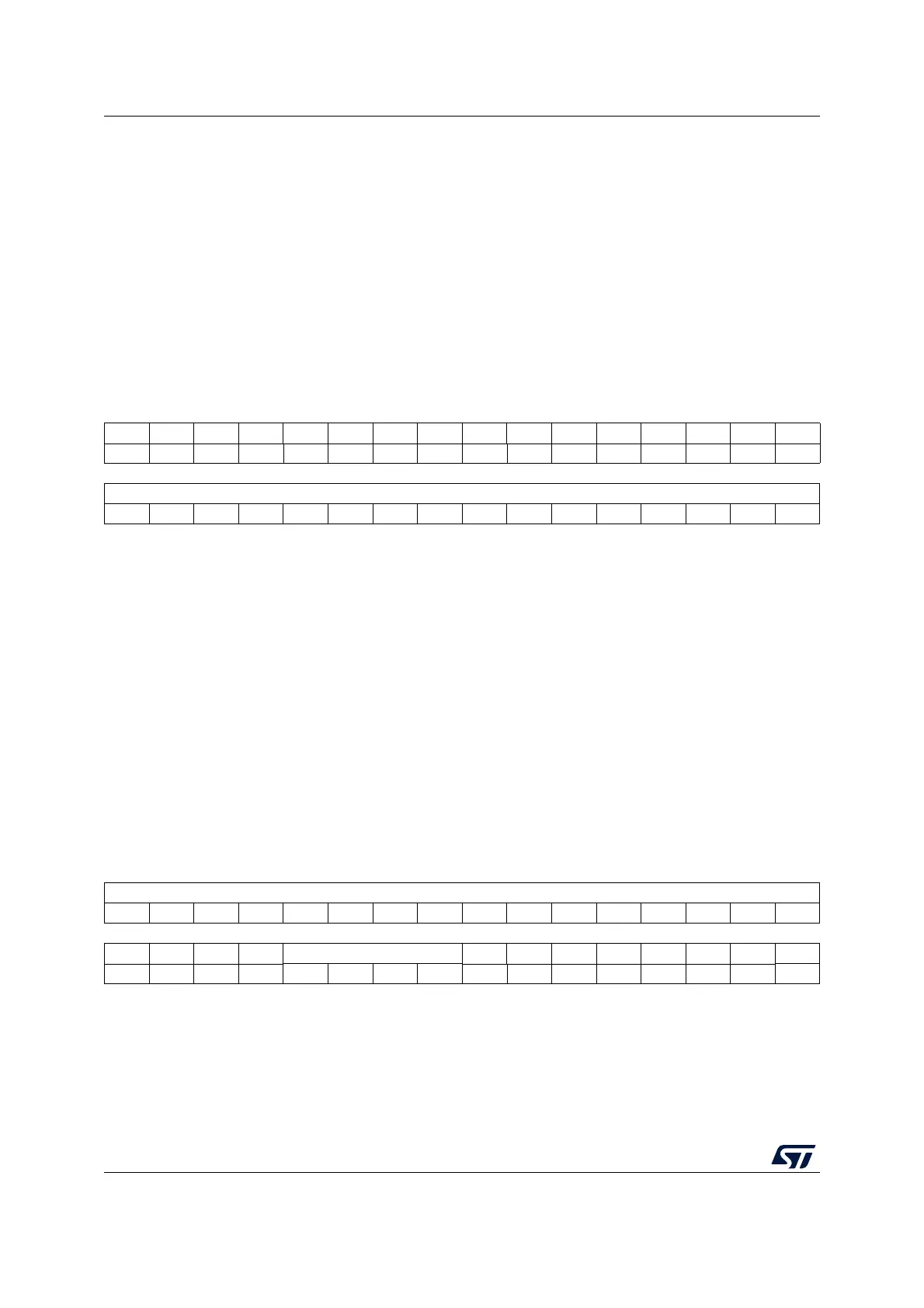

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEY[15:0]

wwwwwwwwwwwwwwww

1514131211109876543210

Res. Res. Res. Res. COREID[3:0] Res. Res. Res. Res. Res. Res. Res. Res.

wwww

Loading...

Loading...