RM0453 Rev 2 237/1454

RM0453 Power control (PWR)

275

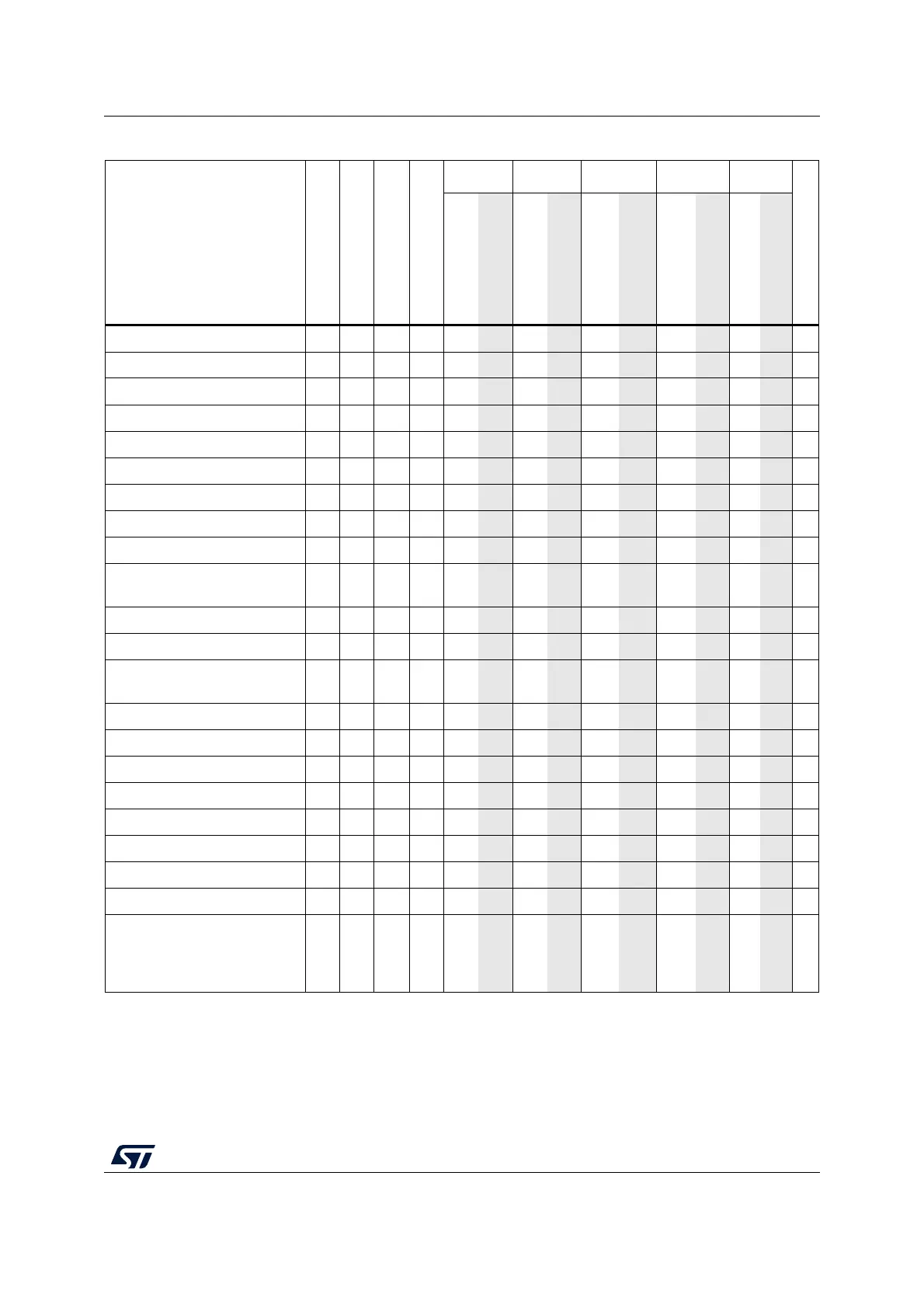

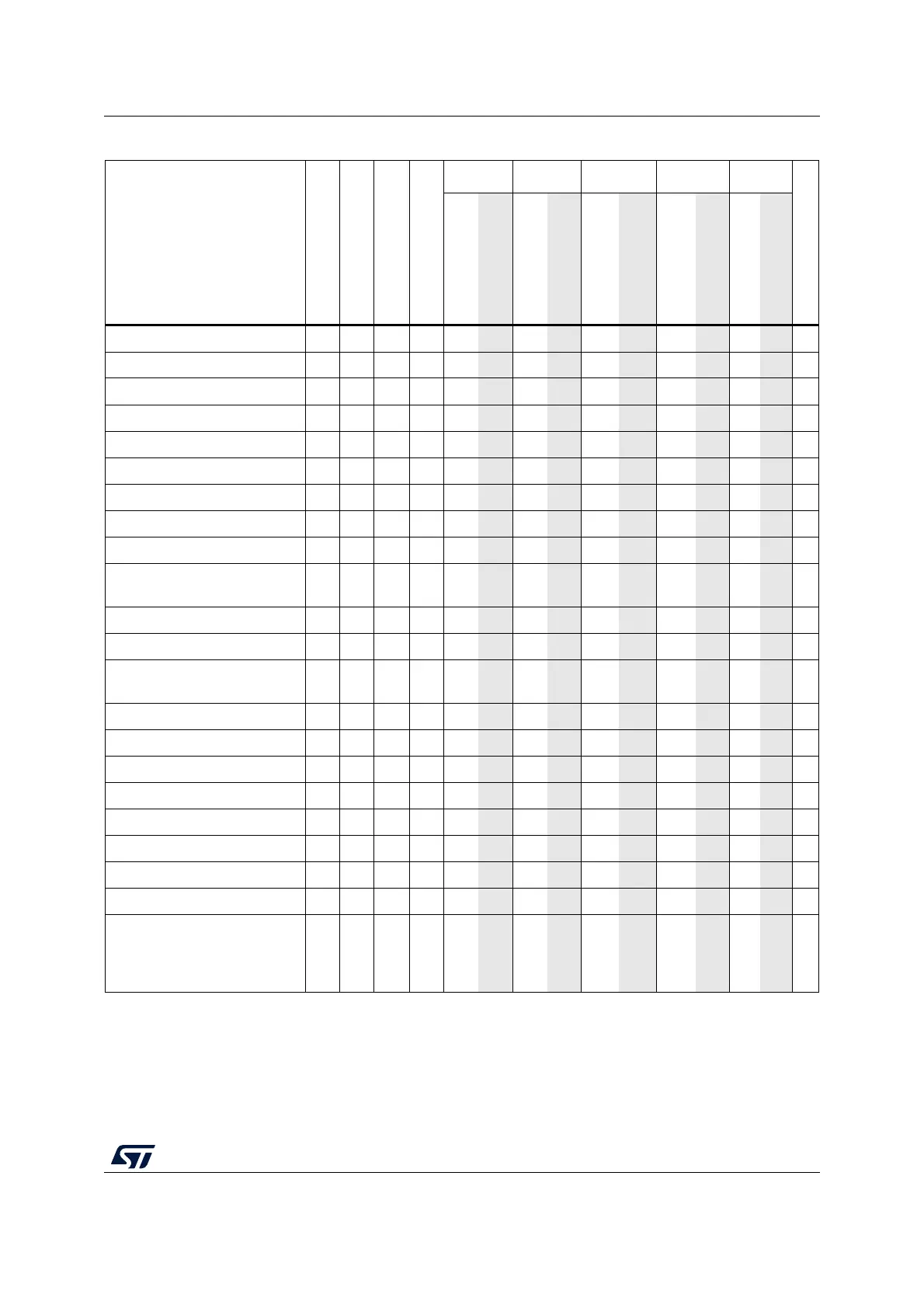

SPI2S2 O O O O R -R-- ------

ADC O O O O R

-R--------

DAC O O O O R

-R--------

VREFBUF O O O O O

-O-R------

COMPx (x = 1, 2) O O O O O

OOOOO-----

Temperature sensor O O O O R

-R--------

Timers (TIMx) x = 1, 2, 16, 17) O O O O R

-R--------

LPTIM1 O O O O O

OOOOO-----

LPTIMx (x = 2, 3) O O O O O

OOO- ------

Independent watchdog

(IWDG)

OOOOOOOOOOOO- --

Window watchdog (WWDG) O O O O R -R-R ------

SysTick timer O O O O R

-R-R------

True random number

generator (RNG)

O

(10)

O

(1

0)

RRR -R-- ------

AES hardware accelerator O O O O R -R-- ------

PKA hardware accelerator O O O O R

-R--------

CRC calculation unit O O O O R

-R-R------

IPCC O R O R R

-R-R------

HSEM O R O R R

-R--------

GTZC TZSC O R O R R

-R-R------

GTZC TZIC O R O R R

-R-R------

EXTI O O O O R

OROR O-----

GPIOs O O O O O OOOO OR

(11)

3

pin

s

(12)

(13)

3

pin

s

(1

2)

-

1. Legend: Y = Yes (enable). O = Optional (disable by default and can be enabled by software). R = data retained.

- = Not available. Gray cells indicate wakeup capability.

2. The SRAM clock can be gated on or off.

3. Flash memory can be placed in power-down mode.

4. The SRAM2 content can optionally be retained when the PWR_CR3.RRS bit is set.

5. Only when the sub-GHz radio is active.

Table 45. Functionalities depending on system operating mode

(1)

(continued)

Peripheral

Run

Sleep

LPRun

LPSleep

Stop 0 Stop 1 Stop 2 Standby Shutdo

VBAT

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

Loading...

Loading...