RM0453 Rev 2 267/1454

RM0453 Power control (PWR)

275

6.6.15 PWR port H pull-up control register (PWR_PUCRH)

This register is not reset when exiting Standby modes and with PWRRST bit in the

RCC_APB1RSTR1 register.

Access: additional APB cycles are needed to access this register versus those needed for a

standard APB access (three for a write and two for a read).

Address offset: 0x058

Reset value: 0x0000 0000

6.6.16 PWR port H pull-down control register (PWR_PDCRH)

This register is not reset when exiting Standby modes and with PWRRST bit in the

RCC_APB1RSTR1 register.

Access: additional APB cycles are needed to access this register versus those needed for a

standard APB access (three for a write and two for a read).

Address offset: 0x05C

Reset value: 0x0000 0000

Bits 15:13 PD[15:13]: Port PC[y] pull-down (y = 13 to 15)

When set, each bit activates the pull-down on PC[y] when both APC bits are set in PWR

control register 3 (PWR_CR3) and in PWR CPU2 control register 3 (PWR_C2CR3).

Bits 12:7 Reserved, must be kept at reset value.

Bits 6:0 PD[6:0]: Port PC[y] pull-down bit y (y = 0 to 6)

When set, each bit activates the pull-down on PC[y] when both APC bits are set in PWR

control register 3 (PWR_CR3) and in PWR CPU2 control register 3 (PWR_C2CR3).

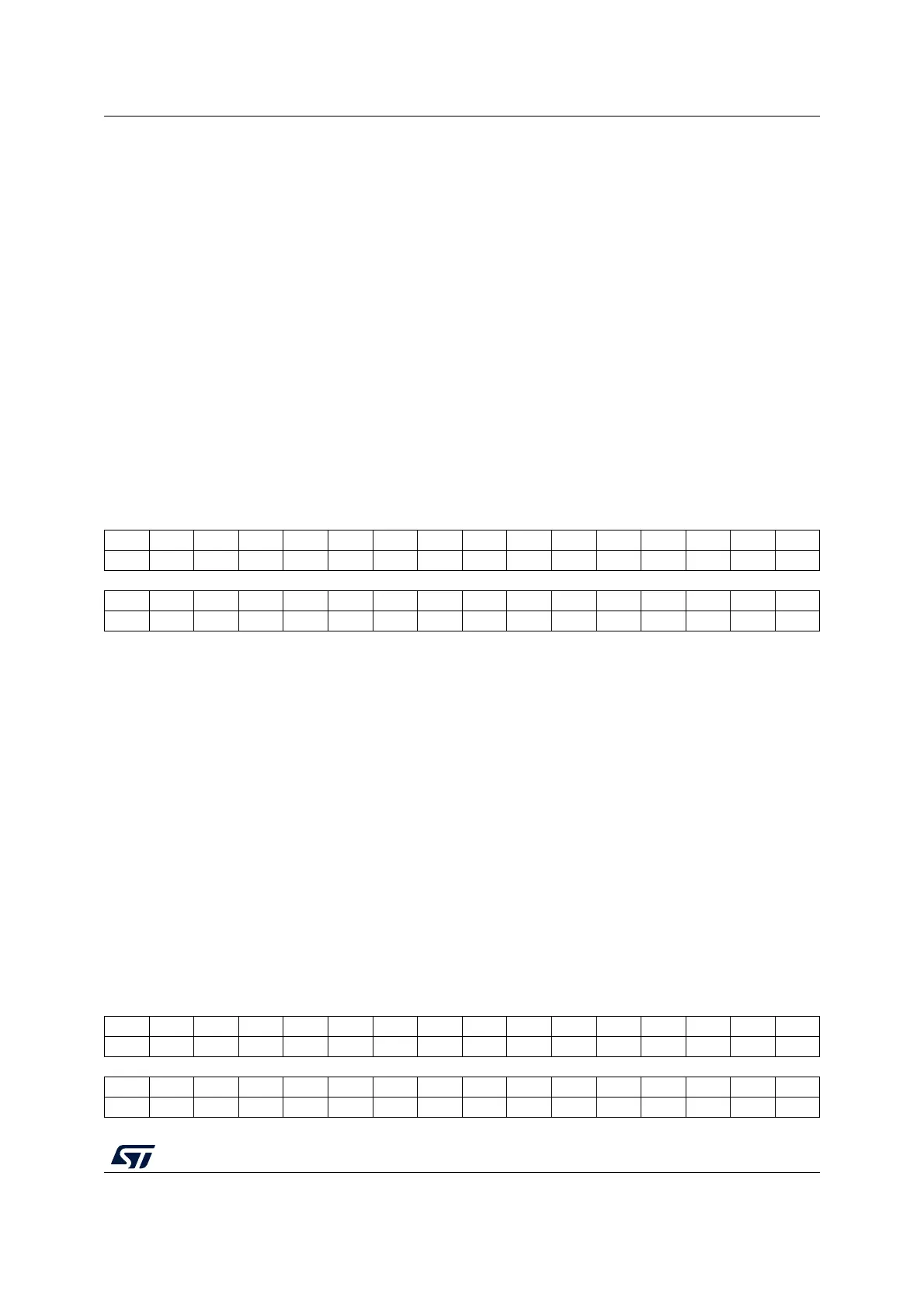

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. PU3 Res. Res. Res.

rw

Bits 31:4 Reserved, must be kept at reset value.

Bit 3 PU3: Port PH[3] pull-up

When set, this bit activates the pull-up on PH[3] when both APC bit are set in PWR control

register 3 (PWR_CR3) and in PWR CPU2 control register 3 (PWR_C2CR3). The pull-up is

not activated if the corresponding PH[3] bit is also set.

Bits 2:0 Reserved, must be kept at reset value.

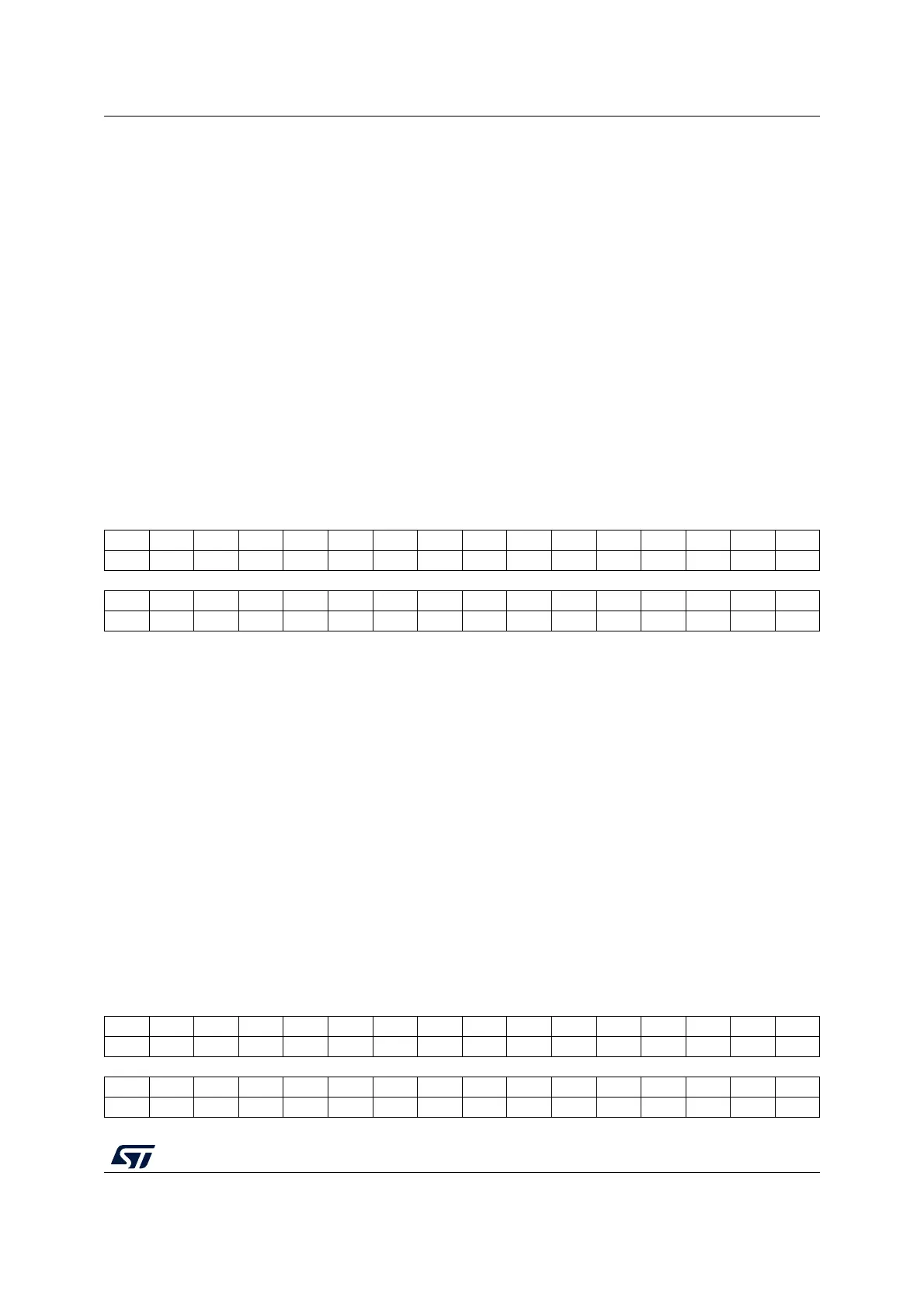

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. PD3 Res. Res. Res.

rw

Loading...

Loading...