Power control (PWR) RM0453

268/1454 RM0453 Rev 2

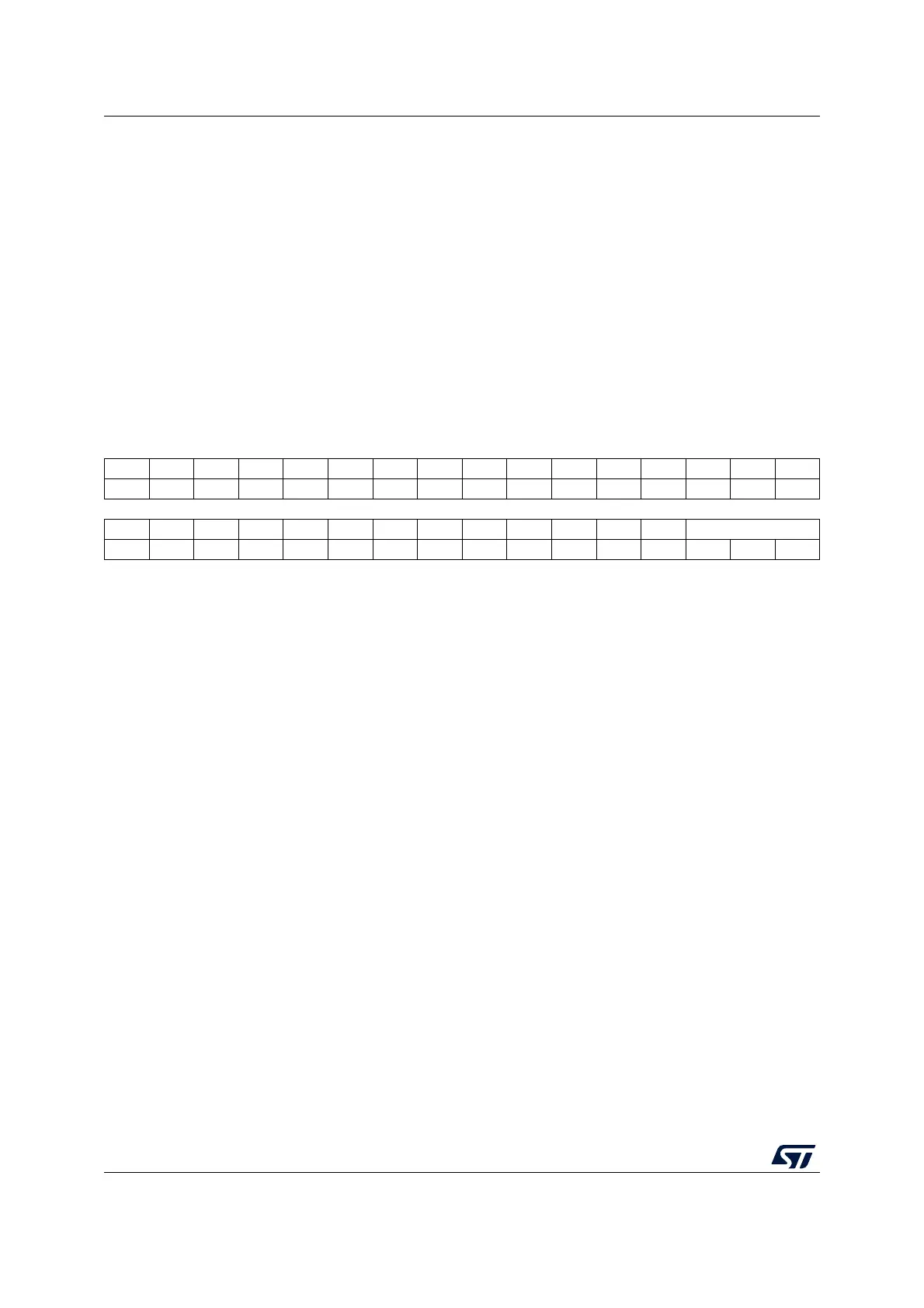

6.6.17 PWR CPU2 control register 1 (PWR_C2CR1)

This register is reset after wakeup from Standby mode, except for bits [2:0].

The register reset value (0x0000 0007) selects Shutdown mode.

Address offset: 0x080

Reset value: 0x0000 0007

Bits 31:4 Reserved, must be kept at reset value.

Bit 3 PD3: Port PH[3] pull-down

When set, this bit activates the pull-down on PH[3] when both APC bits are set in PWR

control register 3 (PWR_CR3) and in PWR CPU2 control register 3 (PWR_C2CR3).

Bits 2:0 Reserved, must be kept at reset value.

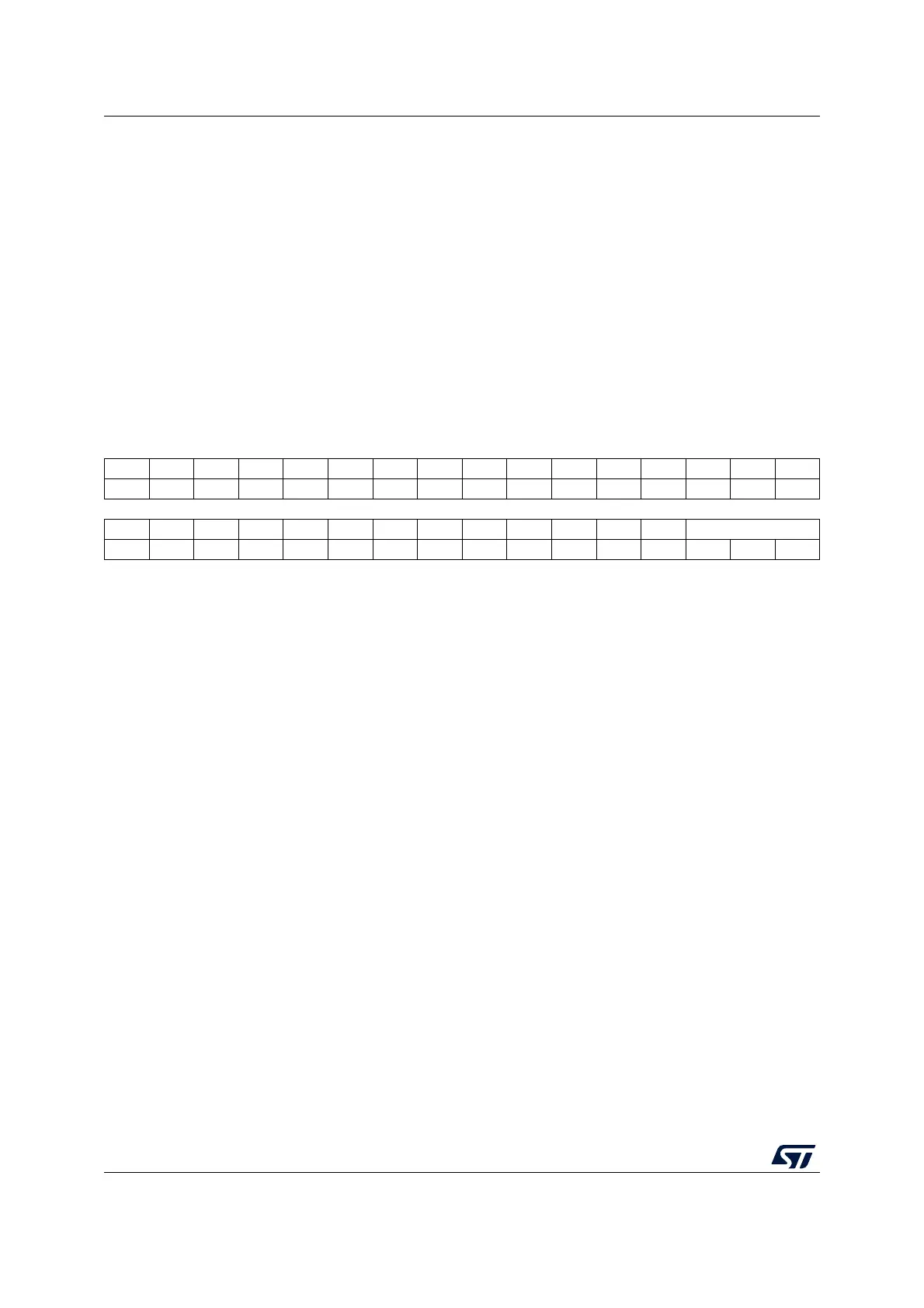

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. FPDS FPDR Res. LPMS[2:0]

rw rw rw rw rw

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 FPDS: Flash memory power-down mode during LPSleep for CPU2

This bit selects whether the Flash memory is in power-down mode or Idle mode when both

CPUs are in Sleep mode. Flash memory is only set in power-down mode when the system is

in LPSleep mode and the PWR_CR1.FPDS bit from CPU1 also allows so.

0: Flash memory in Idle mode when system is in LPSleep mode

1: Flash memory in power-down mode when system is in LPSleep mode

Bit 4 FPDR: Flash memory power-down mode during LPRun for CPU2

This bit can only be written to 1 after unlocking this register bit, by first writing (code 0xC1B0)

into this register (when writing the code register bits are not updated). Selects whether the

Flash memory is in power-down mode or Idle mode when in LPRun mode. (Flash memory

can only be in power-down mode when code is executed from SRAM). Flash memory is only

set in power-down mode when the system is in LPRun mode, and the PWR_CR1.FPDR bit

from CPU1 also allows so.

0: Flash memory in Idle mode when system is in LPRun mode

1: Flash memory in power-down mode when system is in LPRun mode

Loading...

Loading...