RM0453 Rev 2 273/1454

RM0453 Power control (PWR)

275

6.6.22 PWR RSS command register (PWR_RSSCMDR)

This register is only reset by a power-on reset (not reset on NRST and exit from Standby).

Address offset: 0x098

Reset value: 0x0000 0000

Bits 31:16 Reserved, must be kept at reset value.

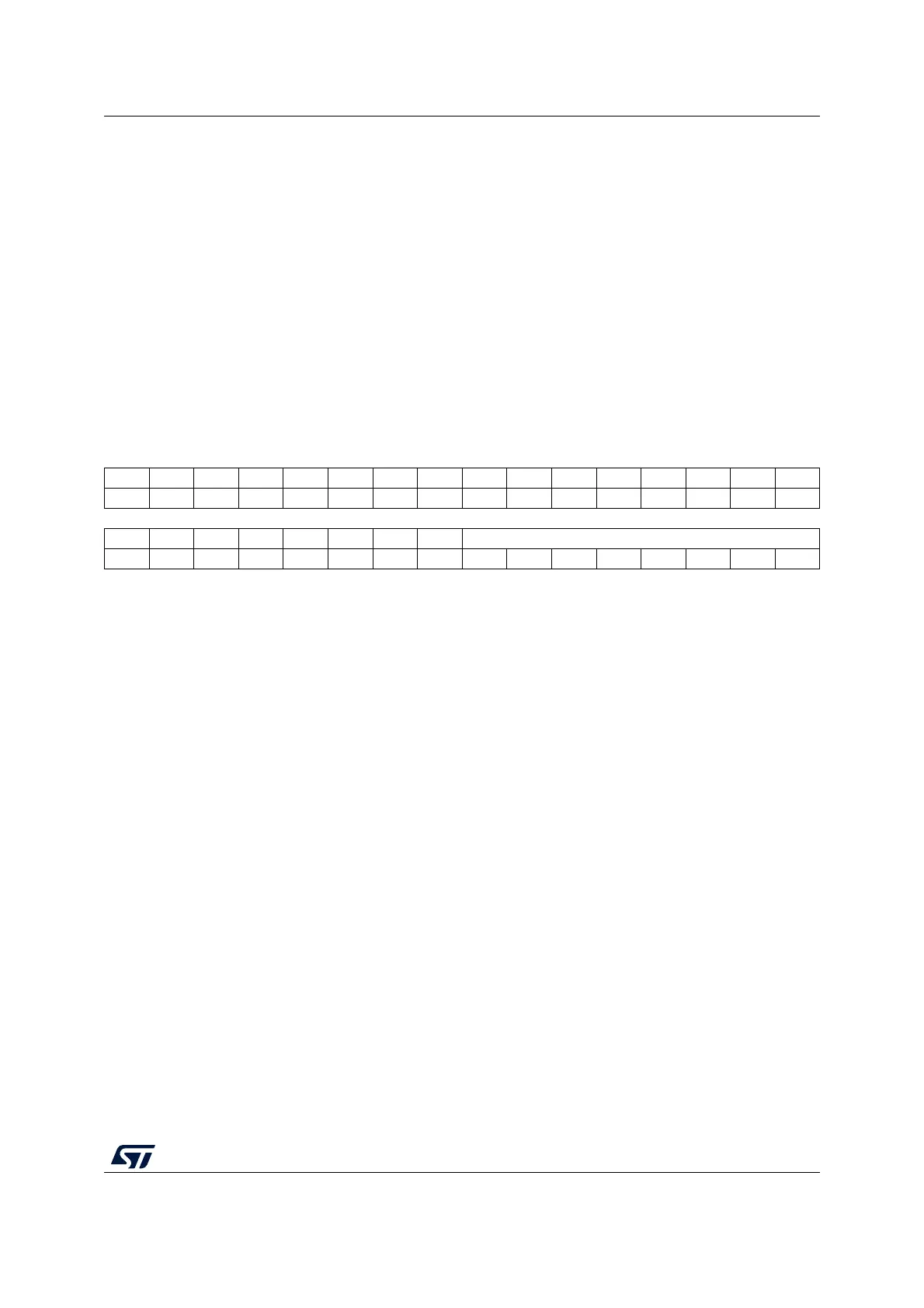

Bit 15 NSS: sub-GHz SPI NSS control

This bit is set and cleared by software and is used to control the sub-GHz SPI NSS level from

software.

0: sub-GHz SPI NSS signal at level low

1: sub-GHz SPI NSS signal is at level high

Bits 14:0 Reserved, must be kept at reset value.

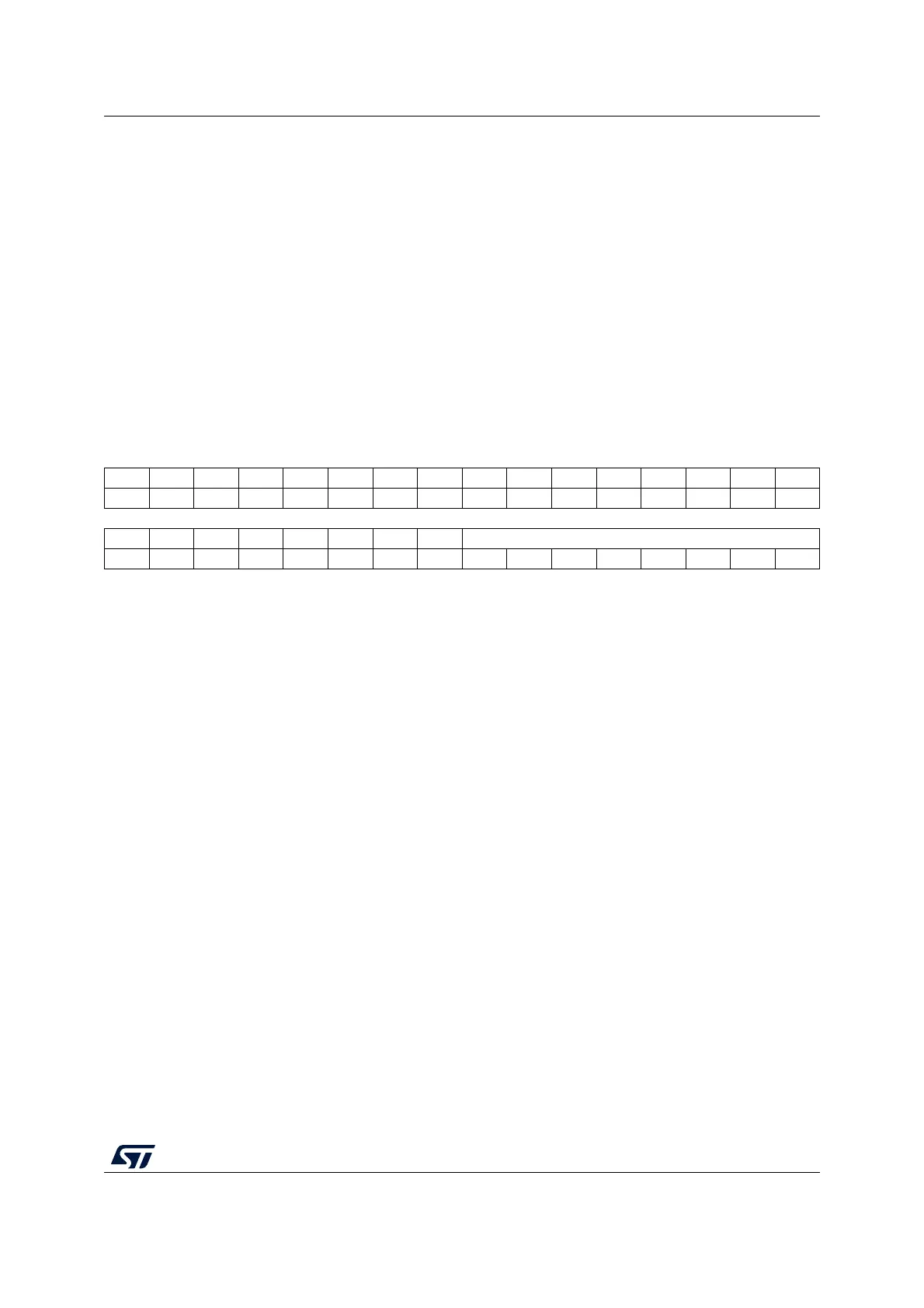

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. RSSCMD[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 RSSCMD[7:0]: RSS command

Define a command to be executed by the RSS.

Loading...

Loading...