RM0453 Rev 2 483/1454

RM0453 DMA request multiplexer (DMAMUX)

497

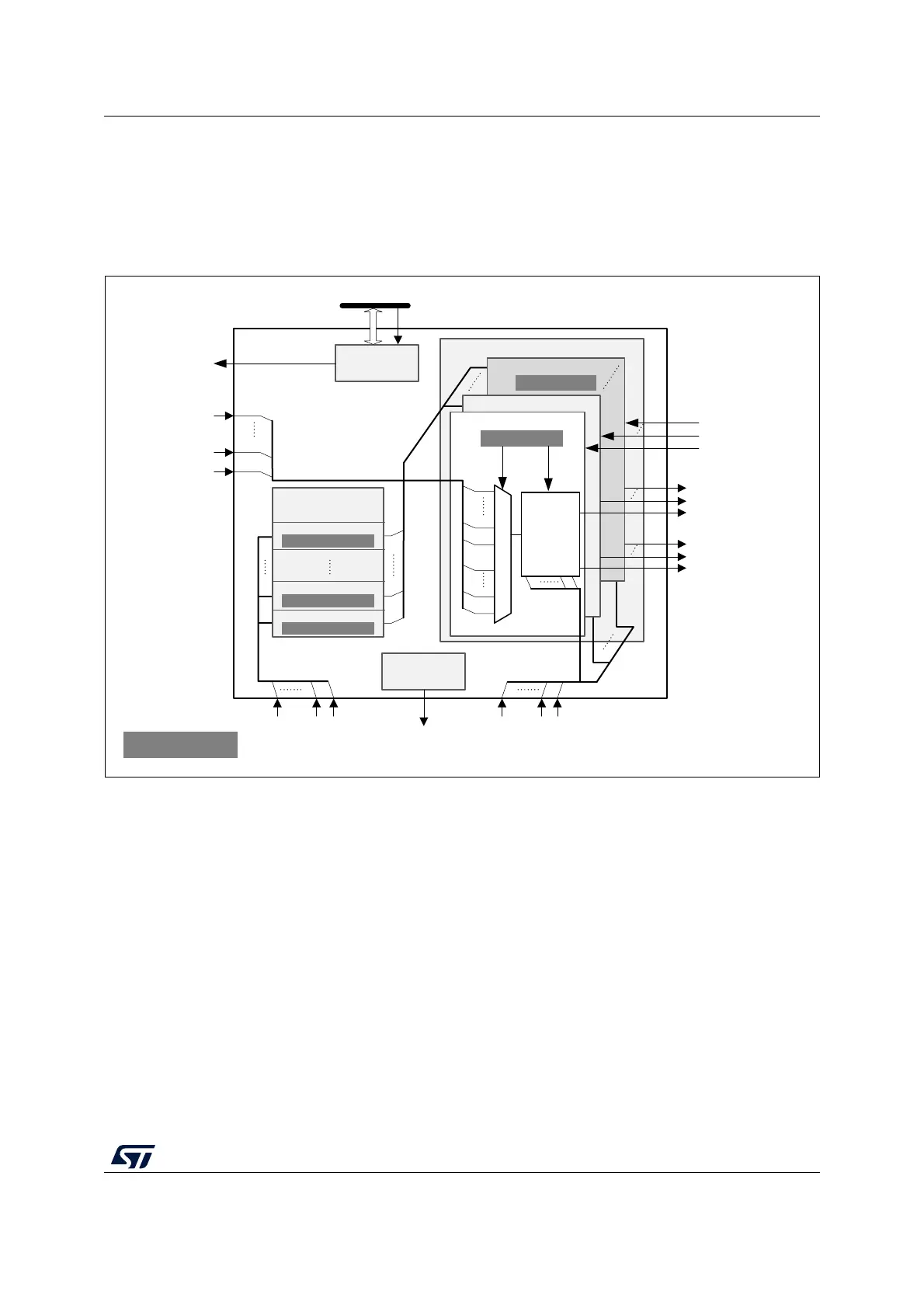

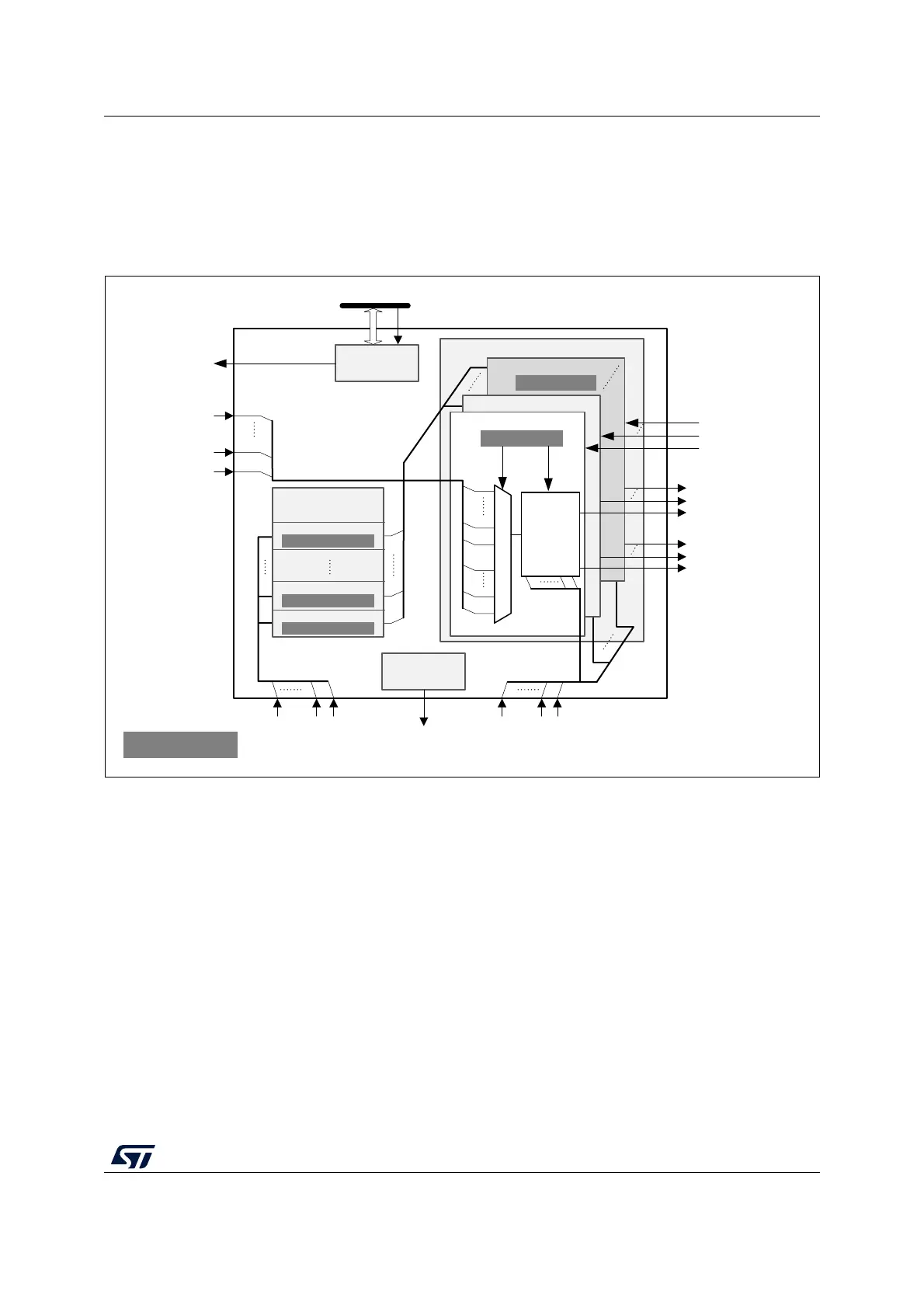

14.4 DMAMUX functional description

14.4.1 DMAMUX block diagram

Figure 50 shows the DMAMUX block diagram.

Figure 50. DMAMUX block diagram

DMAMUX features two main sub-blocks: the request line multiplexer and the request line

generator.

The implementation assigns:

• DMAMUX request multiplexer sub-block inputs (dmamux_reqx) from peripherals

(dmamux_req_inx) and from channels of the DMAMUX request generator sub-block

(dmamux_req_genx)

• DMAMUX request outputs to channels of DMA controllers (dmamux_req_outx)

• Internal or external signals to DMA request trigger inputs (dmamux_trgx)

• Internal or external signals to synchronization inputs (dmamux_syncx)

MS51703V2

DMAMUX_C0CR

Channel 0

0

Channel

select

Ctrl

Channel 1

Channel m

DMAMUX

Request multiplexer

p

n+3

n+2

n+p+2

1

0

n

2

1

n+1

Control registers

1

DMAMUX_CmCR

DMAMUX_RGC0CR

DMAMUX_RGC1CR

DMAMUX_RGCnCR

Channel n

Channel 1

Channel 0

Sync

Request

generator

AHB slave

interface

32-bit AHB bus

dmamux_hclk

Interrupt

interface

Interrupts:

dmamux_sec_ovr_it,

dmamux_nonsec_ovr_it

Synchronization inputs:

dmamux_syncx

Trigger inputs:

dmamux_trgx

DMA requests

to DMA controllers:

dmamux_req_outx

DMA channels events:

dmamux_evtx

DMA requests

from peripherals:

dmamux_req_inx

01s

01

s

0

1

m

0

1

m

01t

dmamux_req_genx

dmamux_reqx

Secure and

privileged state of

the DMA channels:

dma_secmx

dma_privx

0

1

m

To secure

interrupt

controller:

dmamux_ilac

Loading...

Loading...