Inter-processor communication controller (IPCC) RM0453

390/1454 RM0453 Rev 2

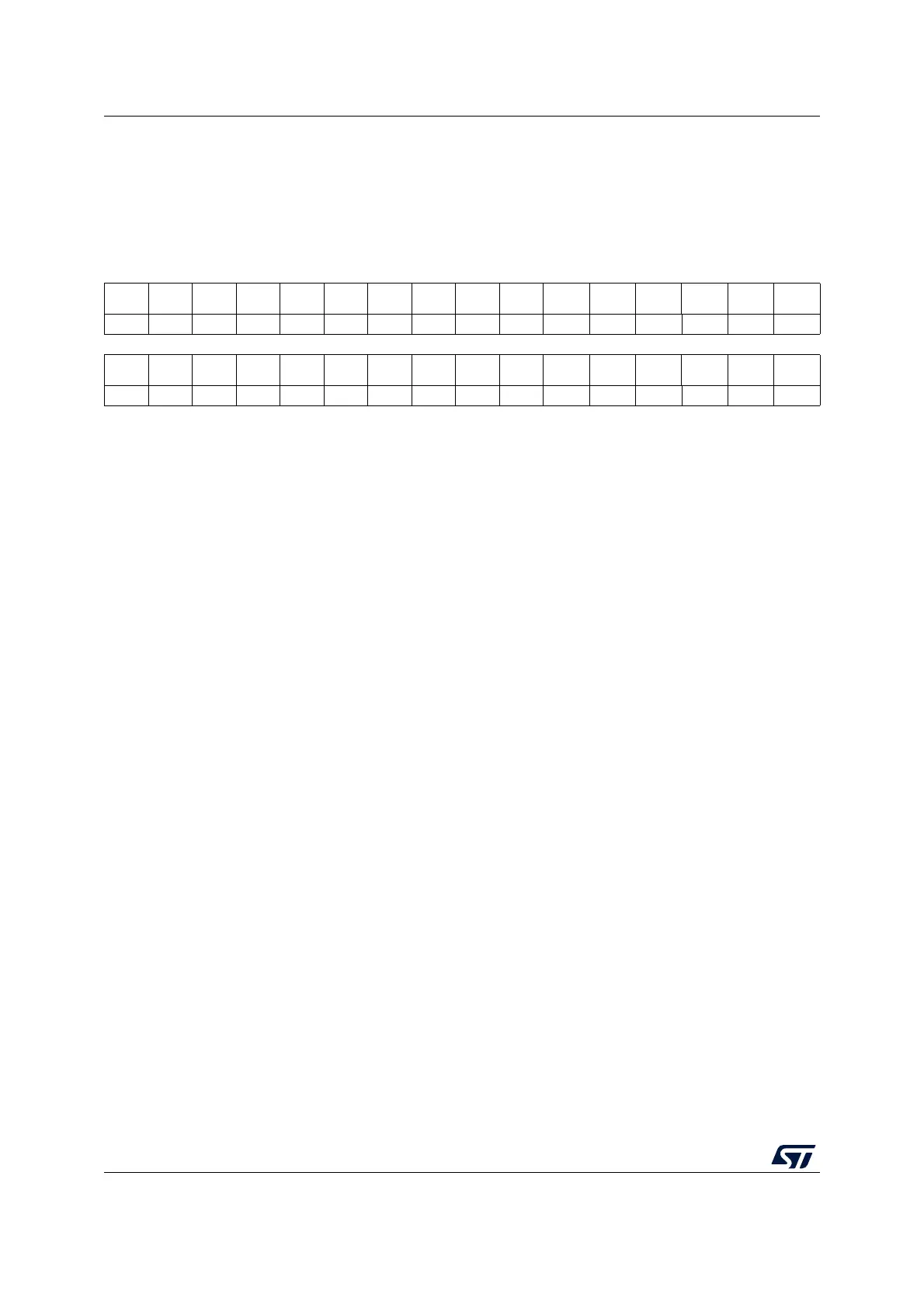

9.4.8 IPCC processor 2 to processor 1 status register

(IPCC_C2TOC1SR)

Address offset: 0x01C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15141312111098765 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CH6F CH5F CH4F CH3F CH2F CH1F

rrrrrr

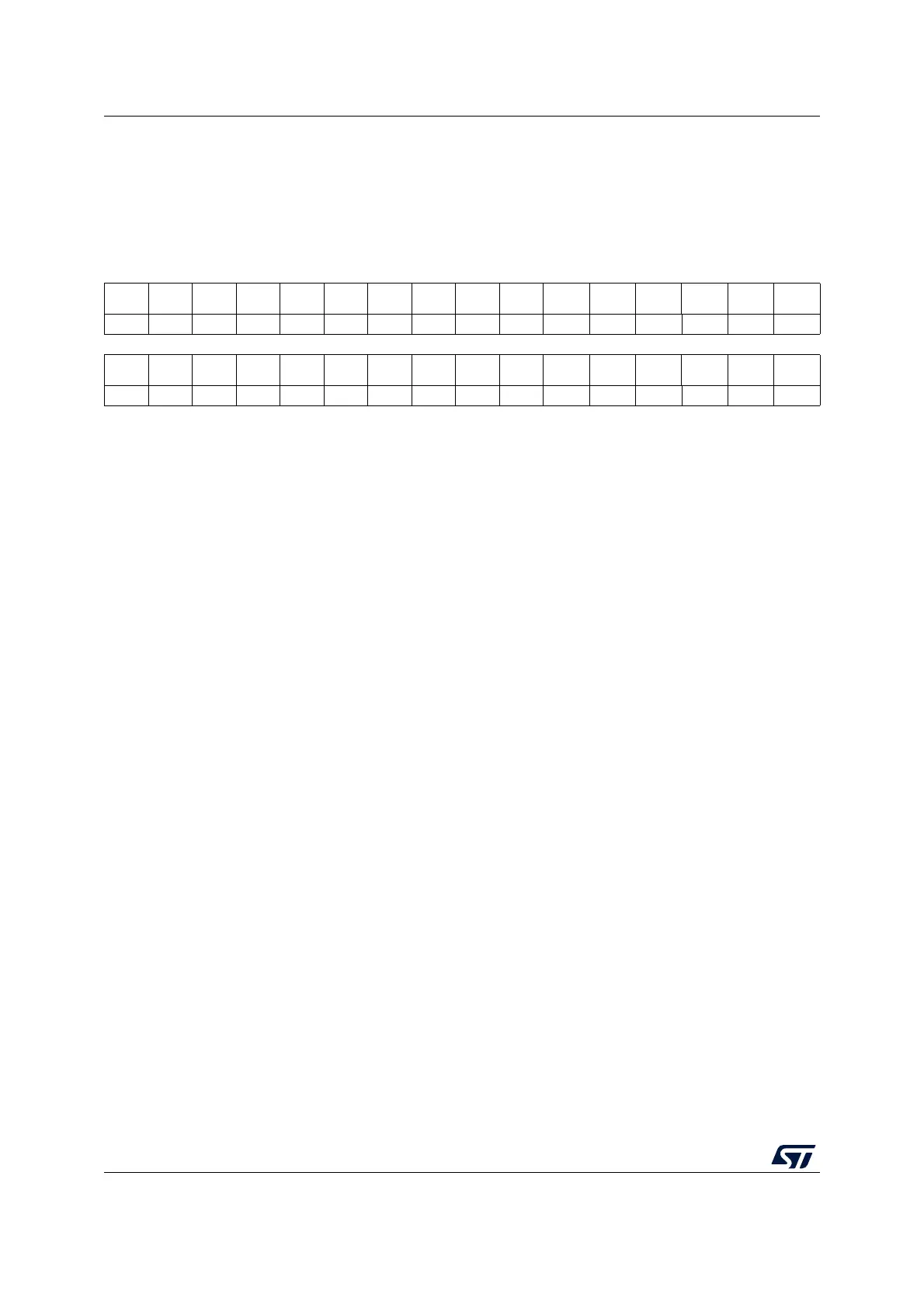

Bits 31:6 Reserved, must be kept at reset value.

Bits 5:0 CHnF: Processor 2 transmit to processor 1 receive channel n status flag before masking (n = 6

to 1)

1: Channel occupied, data can be read by the receiving processor 1.

Generates a channel RX occupied interrupt to processor 1, when unmasked.

0: Channel free, data can be written by the sending processor 2.

Generates a channel TX free interrupt to processor 2, when unmasked.

Loading...

Loading...