Debug support (DBG) RM0453

1360/1454 RM0453 Rev 2

38.7.1 CTI registers

The register file base addresses are 0xE0043000 for CPU1 CTI and 0xF0001000 for CPU2

CTI (not an issue as the CTIs are accessed via different access ports). The registers are the

same for each CTI.

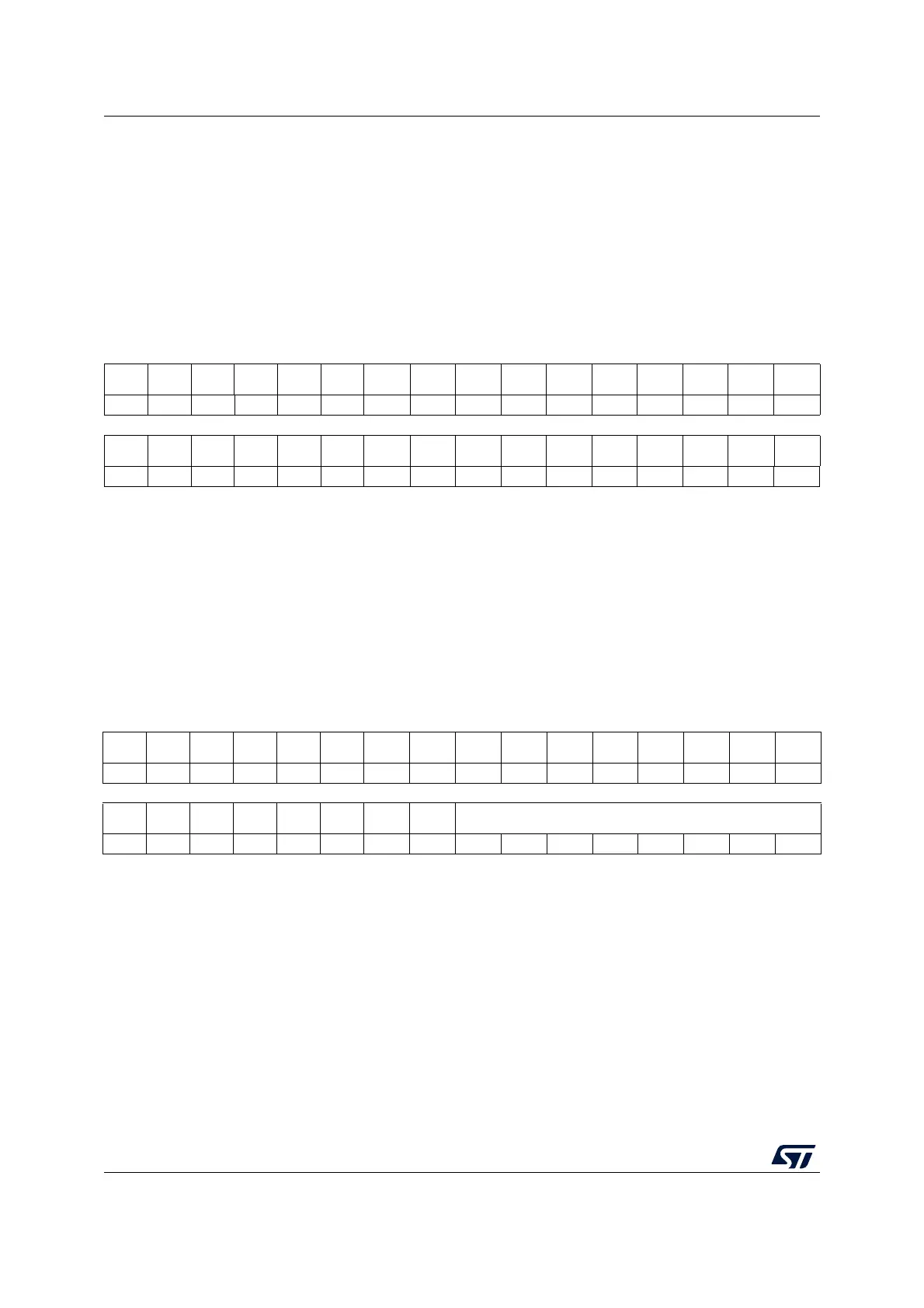

CTI control register (CTI_CONTROLR)

Address offset: 0x000

Reset value: 0x0000 0000

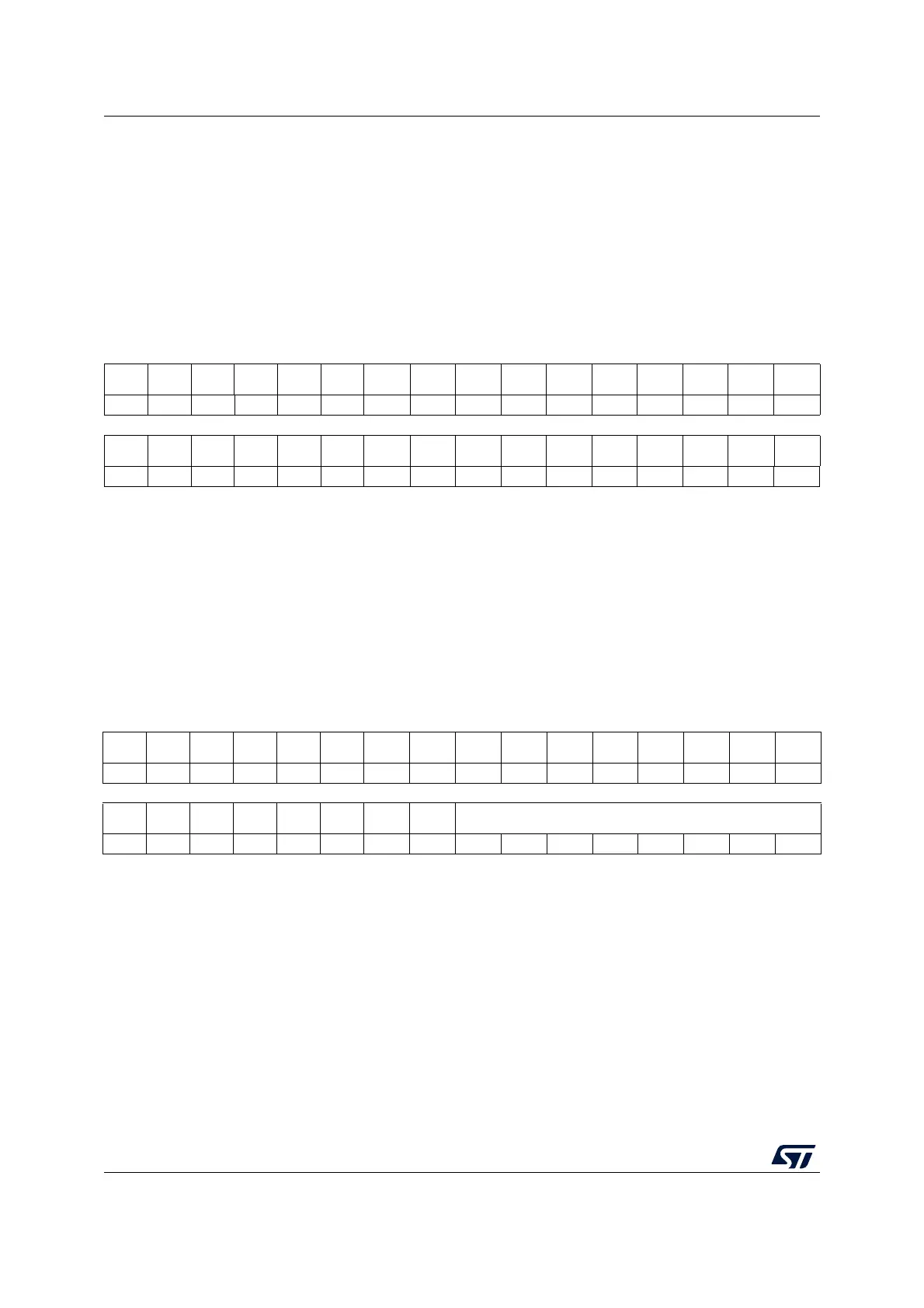

CTI trigger acknowledge register (CTI_INTACKR)

Address offset: 0x010

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. GLBEN

rw

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 GLBEN: global enable

0: Cross-triggering disabled

1: Cross-triggering enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. INTACK[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 INTACK[7:0]: trigger acknowledge

There is one bit of the register for each CTITRIGOUT output. When a 1 is written to a bit in

this register, the corresponding CTITRIGOUT output is acknowledged, causing it to be

cleared.

Loading...

Loading...