Serial peripheral interface / integrated interchip sound (SPI/I2S) RM0453

1290/1454 RM0453 Rev 2

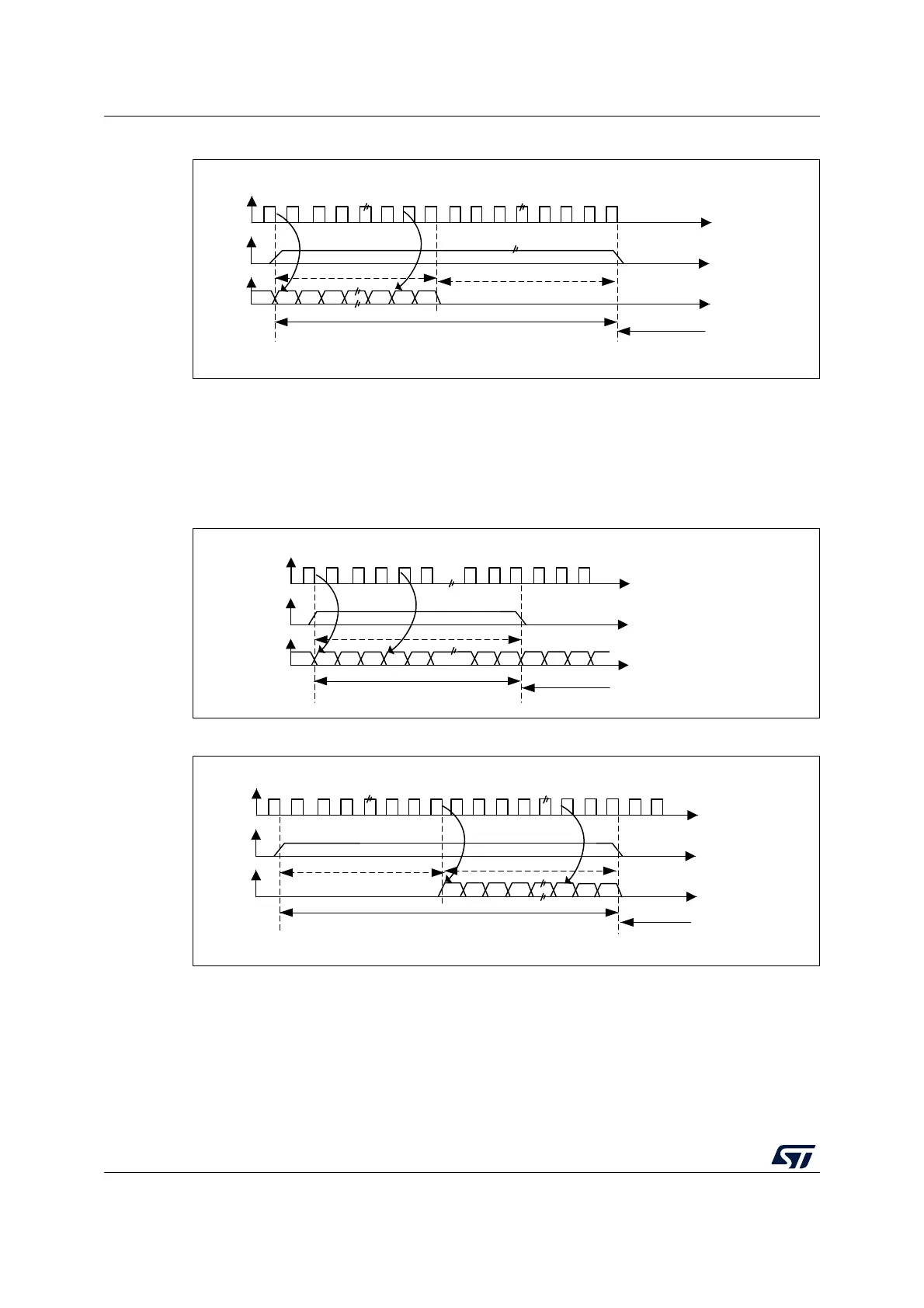

Figure 371. MSB justified 16-bit extended to 32-bit packet frame

LSB justified standard

This standard is similar to the MSB justified standard (no difference for the 16-bit and 32-bit

full-accuracy frame formats).

The sampling of the input and output signals is the same as for the I

2

S Philips standard.

Figure 372. LSB justified 16-bit or 32-bit full-accuracy

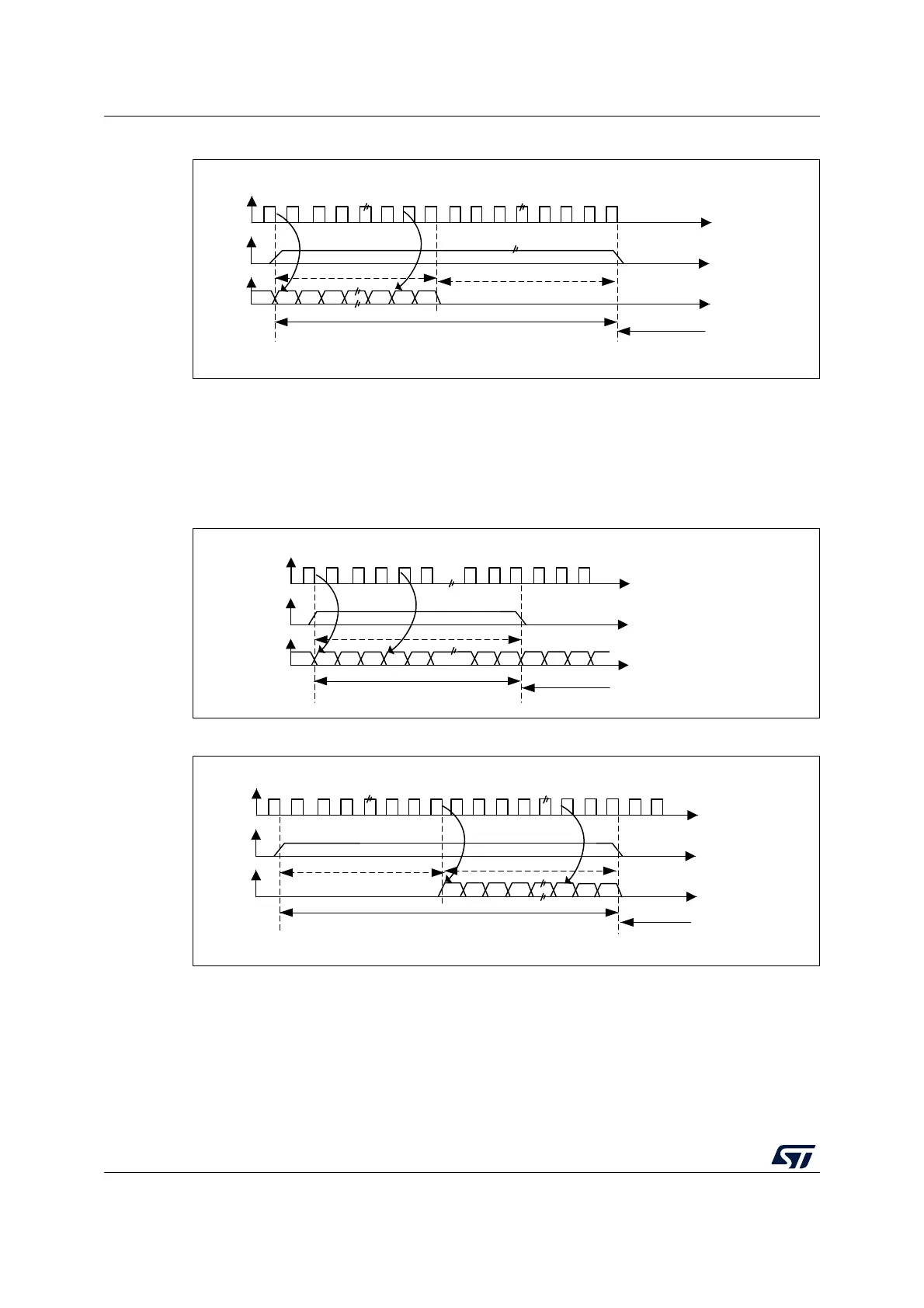

Figure 373. LSB justified 24-bit frame length

• In transmission mode:

If data 0x3478AE have to be transmitted, two write operations to the SPIx_DR register

are required by software or by DMA. The operations are shown below.

MS30102V1

CK

WS

SD

Transmission

Reception

16-bit data

MSB LSB

Channel left 32-bit

Channel right

16-bit remaining

0 forced

MS30103V1

CK

WS

SD

Transmission

Reception

16- or 32-bit data

MSB

LSB

Channel left

Channel right

MSB

MS30104V1

CK

WS

SD

Transmission

Reception

8-bit data

0 forced

MSB

LSB

Channel left 32-bit

Channel right

24-bit remaining

Loading...

Loading...