Debug support (DBG) RM0453

1380/1454 RM0453 Rev 2

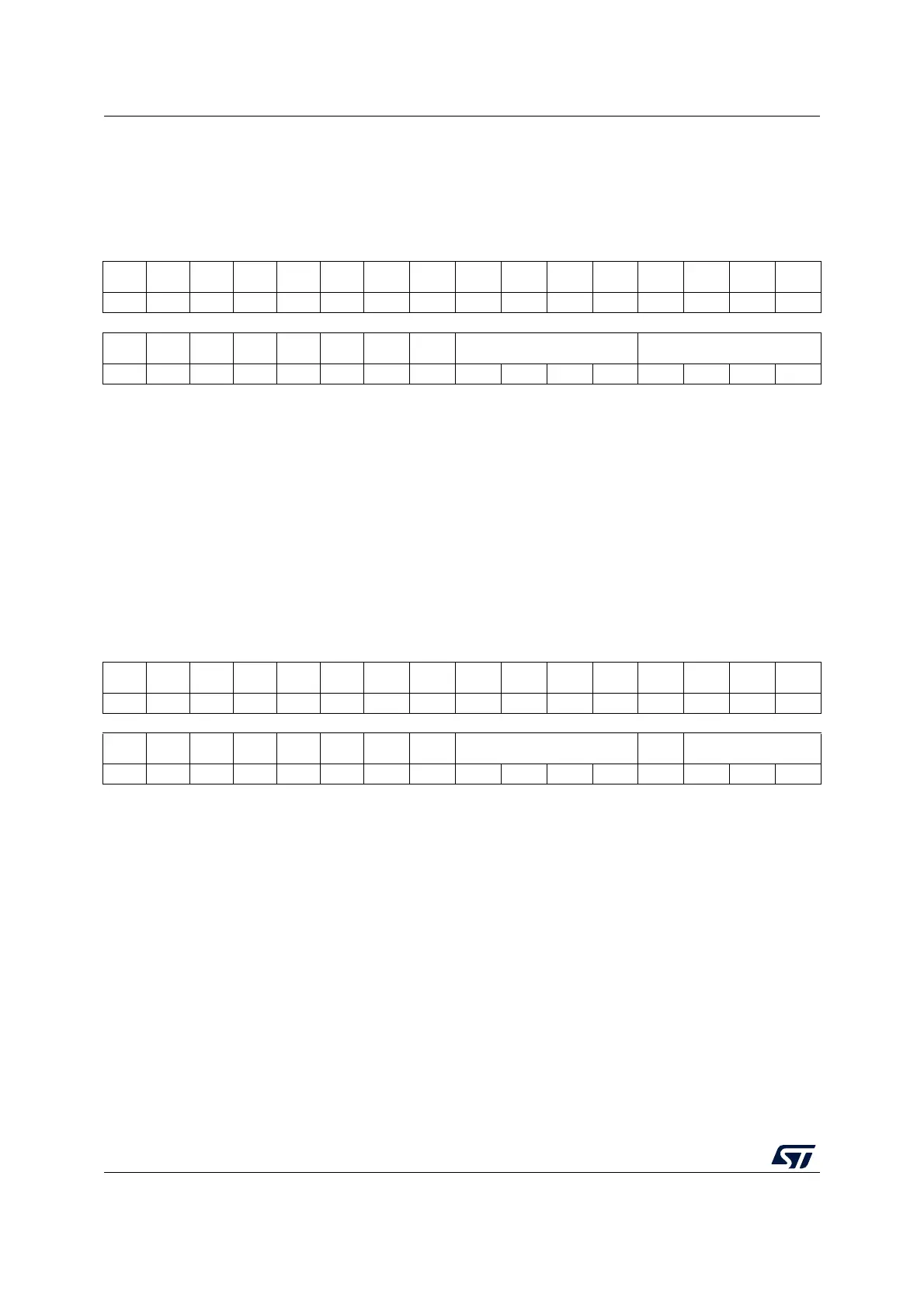

38.8.4 CPU1 ROM CoreSight peripheral identity register 1 (ROM_PIDR1)

Address offset: 0xFE4

Reset value: 0x0000 0004

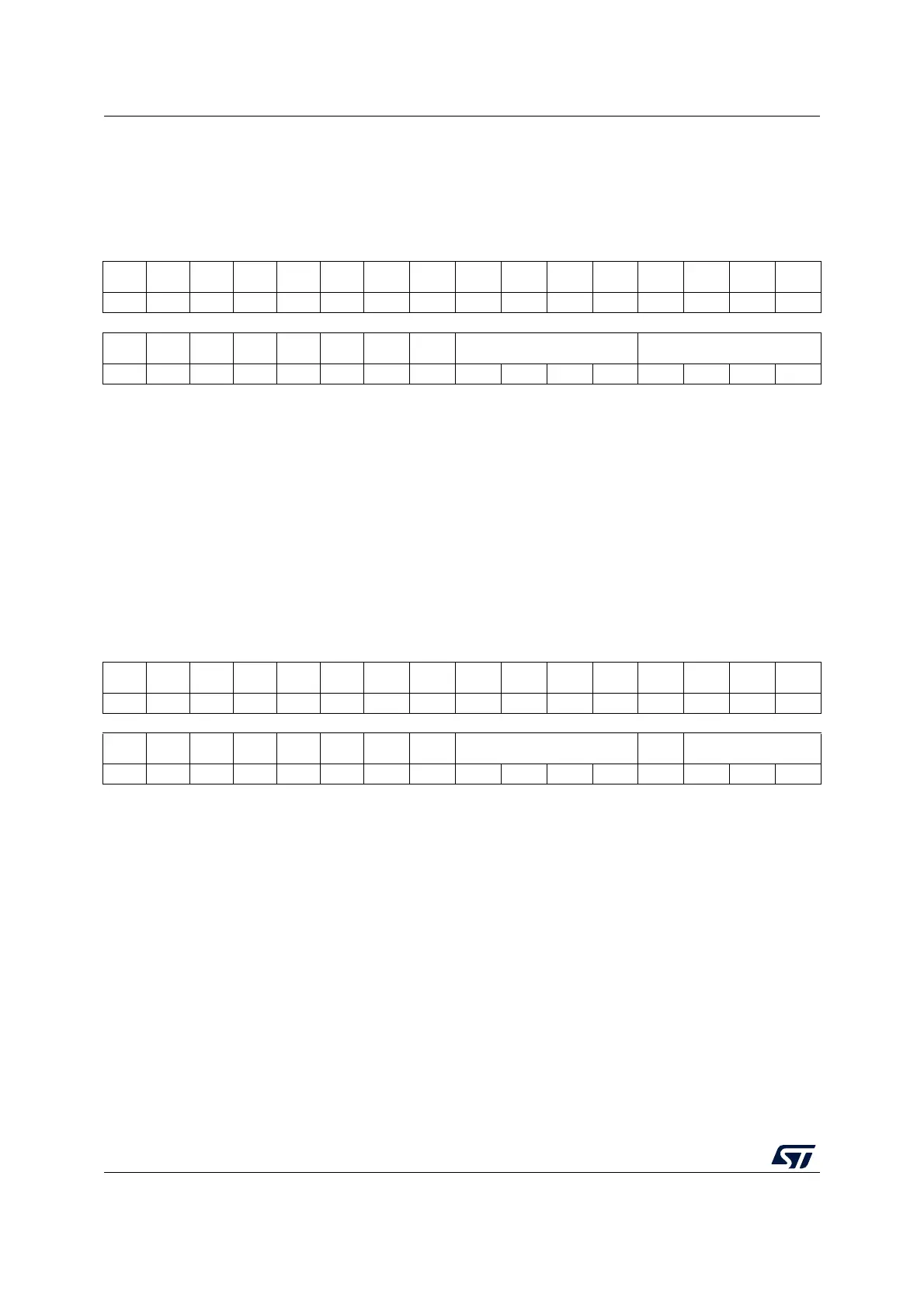

38.8.5 CPU1 ROM CoreSight peripheral identity register 2 (ROM_PIDR2)

Address offset: 0xFE8

Reset value: 0x0000 000A

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. JEP106ID[3:0] PARTNUM[11:8]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 JEP106ID[3:0]: JEP106 identity code bits [3:0]

0x0: STMicroelectronics JEDEC code

Bits 3:0 PARTNUM[11:8]: part number bits [11:8]

0x4: STM32WL5x

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. REVISION[3:0] JEDEC JEP106ID[6:4]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 REVISION[3:0]: component revision number

0x0: rev r0p0

Bit 3 JEDEC: JEDEC assigned value

1: Designer ID specified by JEDEC

Bits 2:0 JEP106ID[6:4]: JEP106 identity code bits [6:4]

0x2: STMicroelectronics JEDEC code

Loading...

Loading...