Debug support (DBG) RM0453

1428/1454 RM0453 Rev 2

Refer to Section 38.13: CPU2 ROM tables for the register boundary addresses.

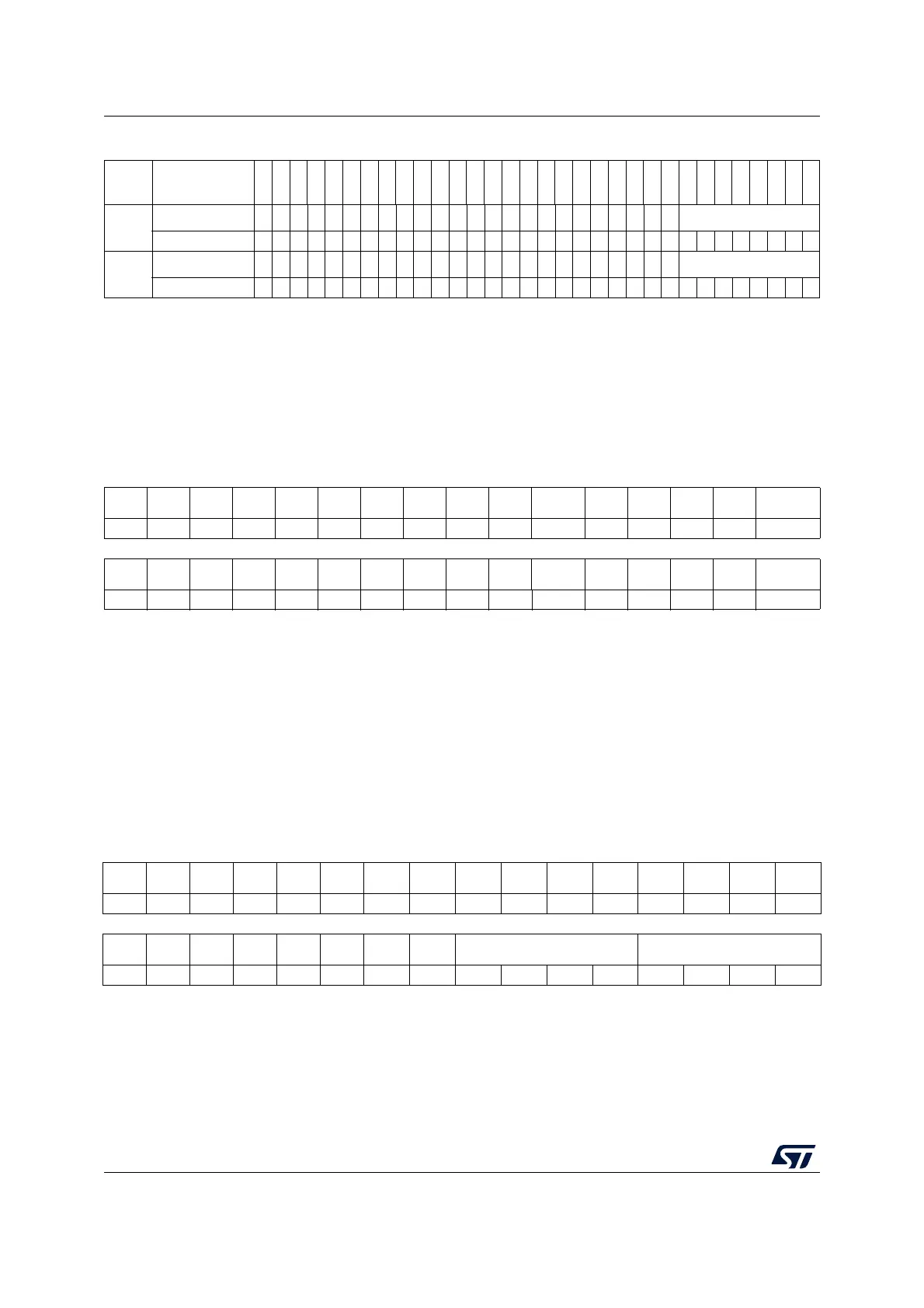

38.13.12 CPU2 ROM2 memory type register (C2ROM2_MEMTYPER)

Address offset: 0xFCC

Reset value: 0x0000 0001

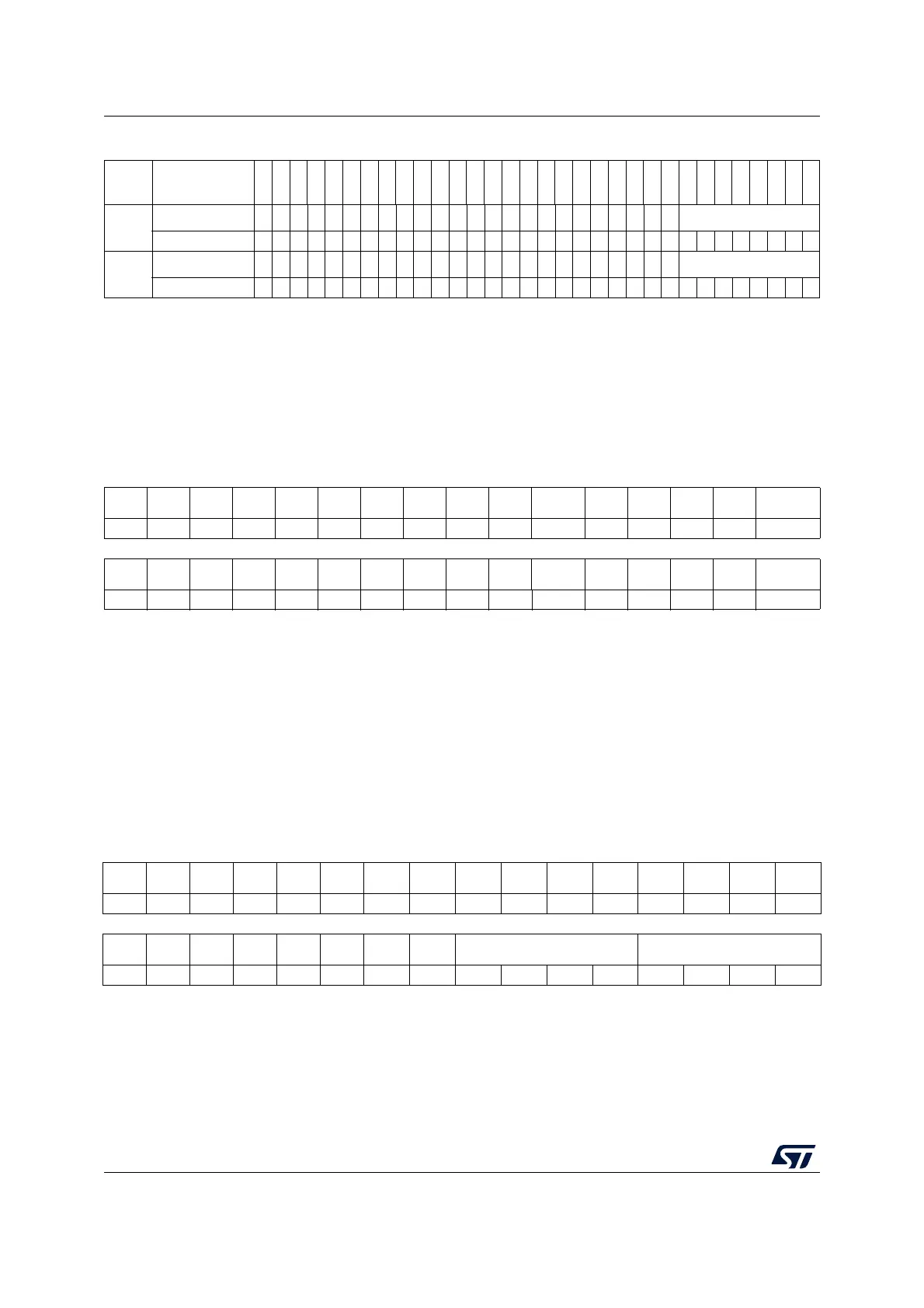

38.13.13 CPU2 ROM2 CoreSight peripheral identity register 4

(C2ROM2_PIDR4)

Address offset: 0xFD0

Reset value: 0x0000 0004

0xFF8

C2ROM1_CIDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[19:12]

Reset value 00000101

0xFFC

C2ROM1_CIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[27:20]

Reset value 10110001

Table 285. CPU2 processor ROM table register map and reset values (continued)

Offset Register name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. SYSMEM

r

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 SYSMEM: system memory

1: System memory present on this bus

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. F4KCOUNT[3:0] JEP106CON[3:0]

rrrrrrrr

Loading...

Loading...