RM0453 Rev 2 1233/1454

RM0453 Low-power universal asynchronous receiver transmitter (LPUART)

1257

36.7 LPUART registers

Refer to Section 1.2 on page 58 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by words (32 bits).

36.7.1 LPUART control register 1 [alternate] (LPUART_CR1)

Address offset: 0x00

Reset value: 0x0000 0000

The same register can be used in FIFO mode enabled (this section) and FIFO mode

disabled (next section).

FIFO mode enabled

1. The LPUART can wake up the device from Stop mode only if the peripheral instance supports the Wakeup from Stop mode

feature. Refer to Section 36.3: LPUART implementation for the list of supported Stop modes.

2. RXFF flag is asserted if the LPUART receives n+1 data (n being the RXFIFO size): n data in the RXFIFO and 1 data in

LPUART_RDR. In Stop mode, LPUART_RDR is not clocked. As a result, this register is not written and once n data are

received and written in the RXFIFO, the RXFF interrupt is asserted (RXFF flag is not set).

3. When OVRDIS = 0.

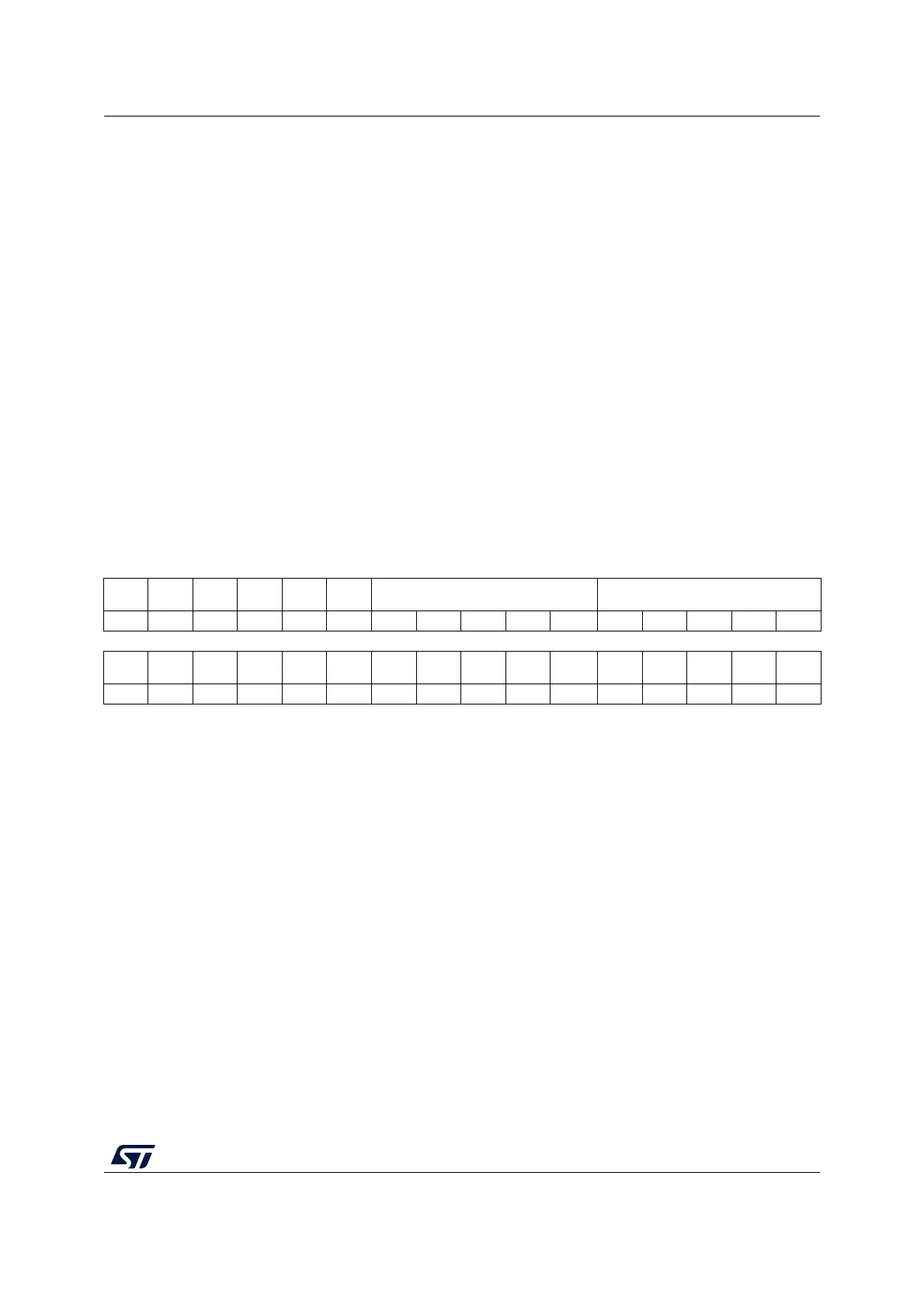

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RXF

FIE

TXFEIE

FIFO

EN

M1 Res. Res. DEAT[4:0] DEDT[4:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

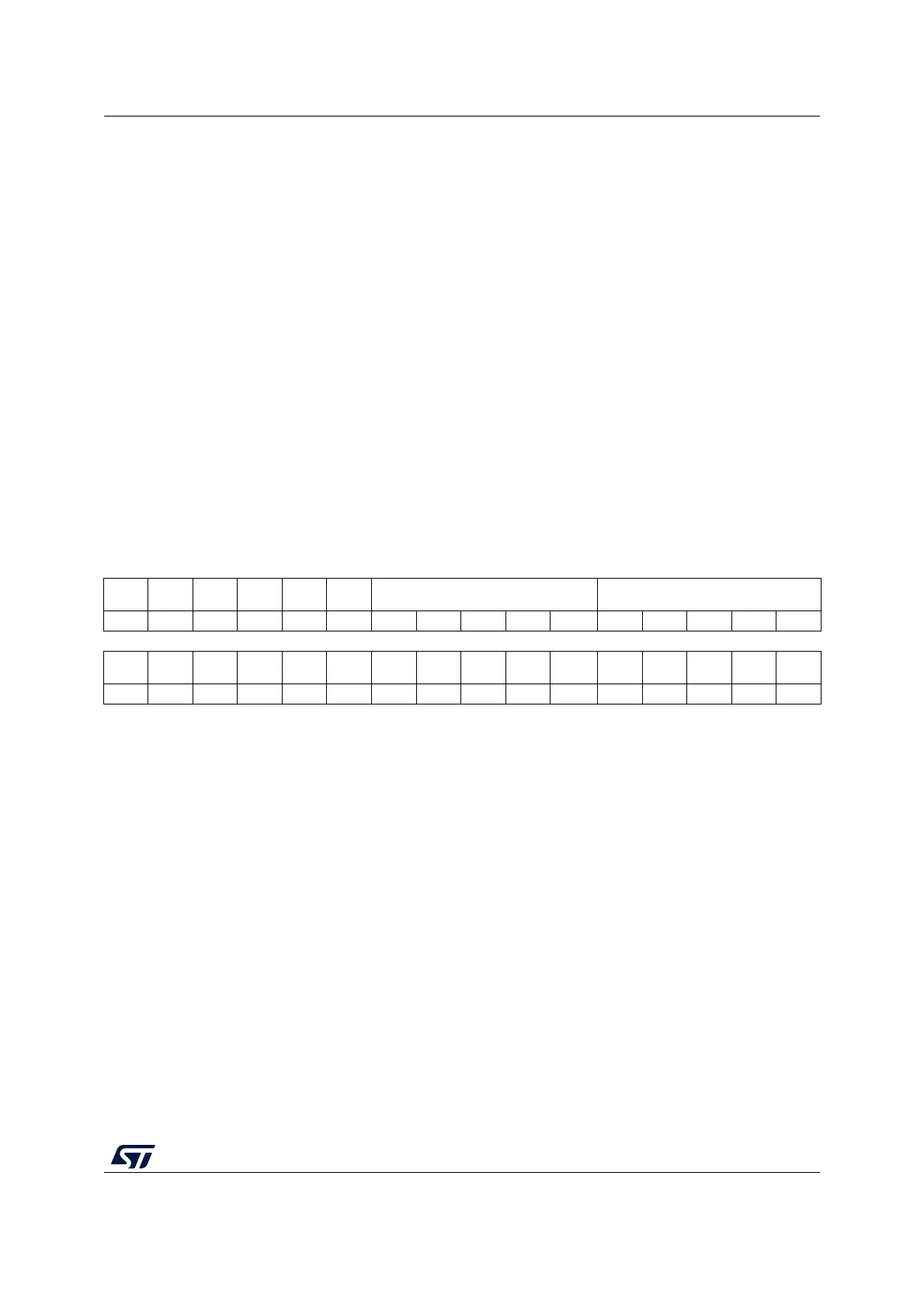

1514131211109876 5 43210

Res. CMIE MME M0 WAKE PCE PS PEIE

TXFN

FIE

TCIE

RXFN

EIE

IDLEIE TE RE UESM UE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 RXFFIE:RXFIFO Full interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated when RXFF = 1 in the LPUART_ISR register

Bit 30 TXFEIE:TXFIFO empty interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated when TXFE = 1 in the LPUART_ISR register

Bit 29 FIFOEN:FIFO mode enable

This bit is set and cleared by software.

0: FIFO mode is disabled.

1: FIFO mode is enabled.

Loading...

Loading...