RM0453 Rev 2 1433/1454

RM0453 Debug support (DBG)

1441

Refer to Section 38.13: CPU2 ROM tables for the register boundary addresses.

38.14 CPU2 breakpoint unit (BPU)

The BPU allows hardware breakpoints to be set. It contains eight comparators which

monitor the instruction fetch address and return a breakpoint instruction when a match is

detected.The CPU2 PBU does not support Flash memory patch functionality.

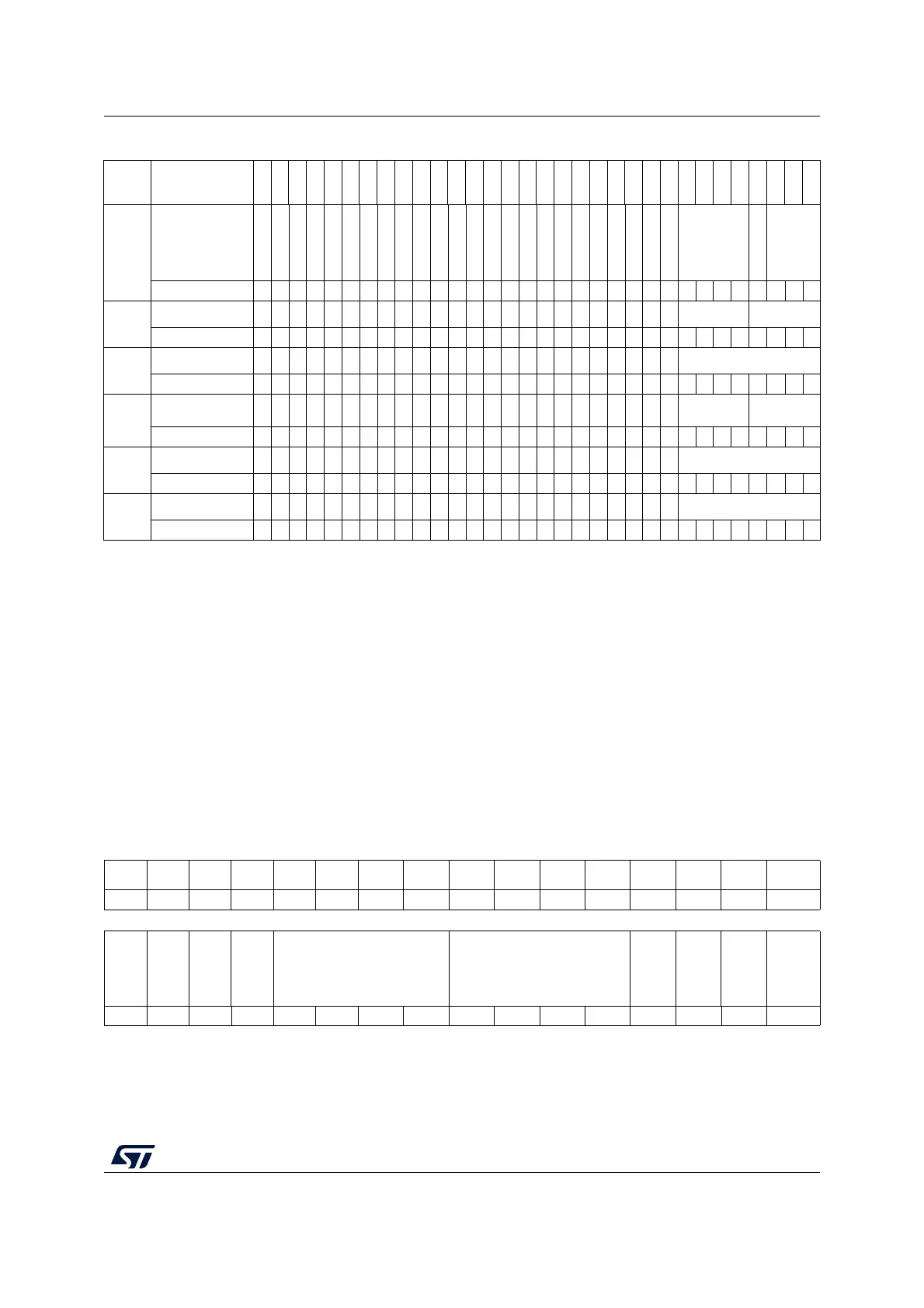

38.14.1 BPU control register (BPU_CTRLR)

Address offset: 0x000

Reset value: 0x0000 0080

0xFE8

C2ROM2_PIDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

REVISION[3:0]

JEDEC

JEP106ID[6:4]

Reset value 00001011

0xFEC

C2ROM2_PIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

REVAND[3:0] CMOD[3:0]

Reset value 00000000

0xFF0

C2ROM2_CIDR0

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[7:0]

Reset value 00001101

0xFF4

C2ROM2_CIDR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CLASS[3:0]

PREAMBLE

[11:8]

Reset value 00010000

0xFF8

C2ROM2_CIDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[19:12]

Reset value 00000101

0xFFC

C2ROM2_CIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[27:20]

Reset value 10110001

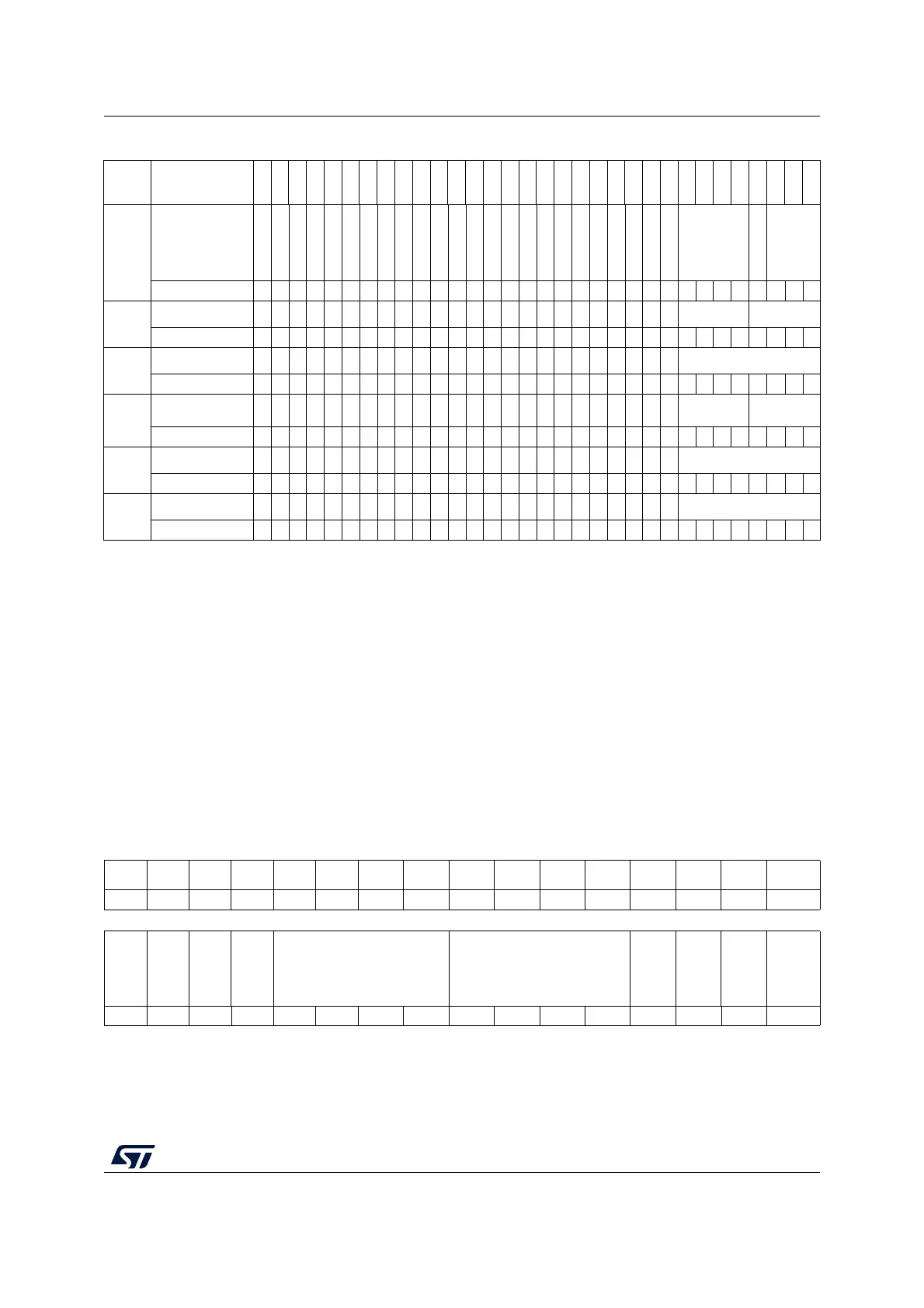

Table 286. CPU2 ROM table register map and reset values (continued)

Offset Register name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

151413121110987654321 0

Res.

NUM_CODE6

NUM_CODE5

NUM_CODE4

NUM_LIT[3:0] NUM_CODE[3:0]

Res. Res.

KEY ENABLE

rrrrrrrrrrr rwrw

Loading...

Loading...