Debug support (DBG) RM0453

1326/1454 RM0453 Rev 2

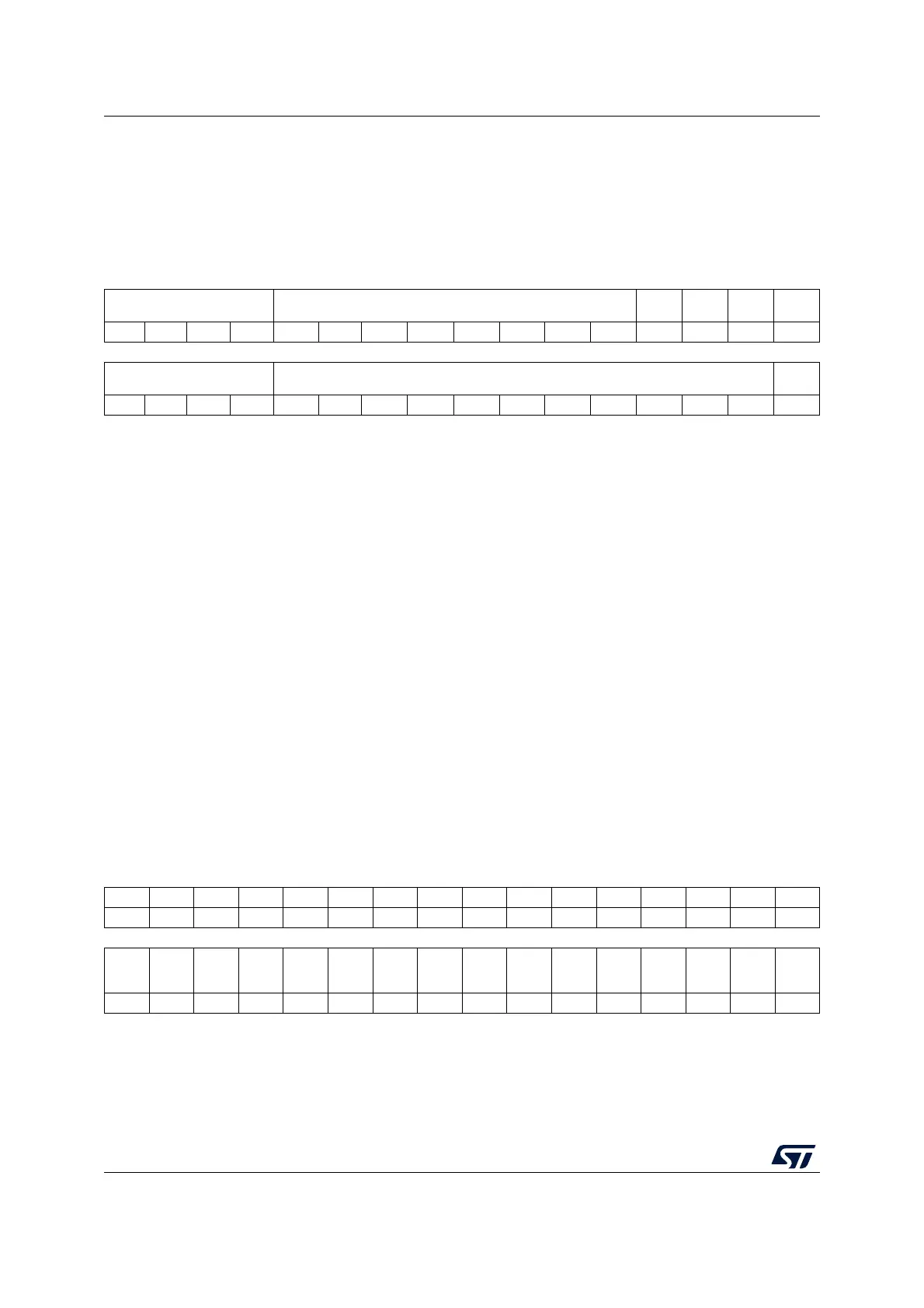

38.4.1 DP identification register (DP_DPIDR)

Address offset: 0x00

Reset value: 0x5BA0 2477

Read only

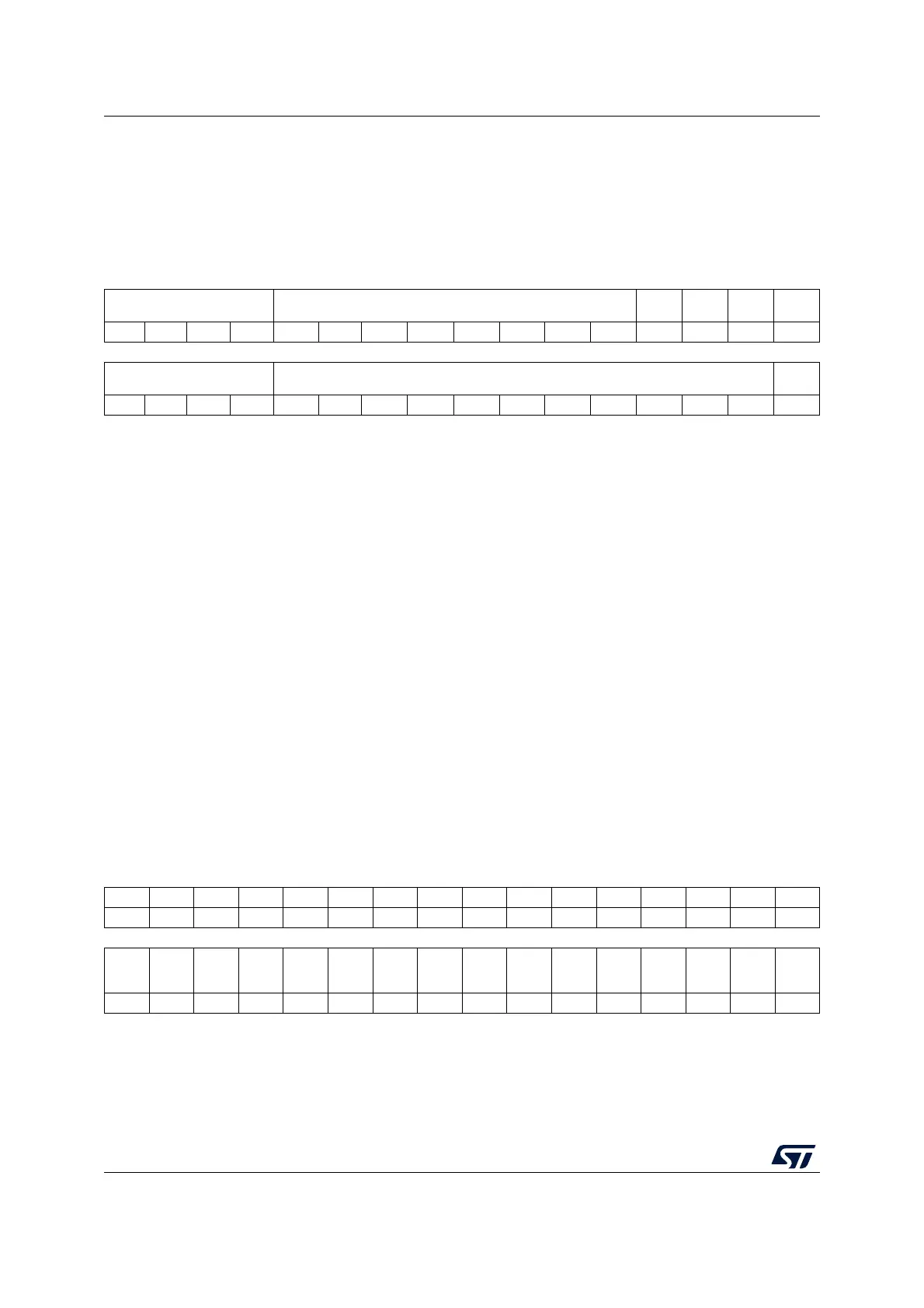

38.4.2 DP abort register (DP_ABORTR)

Address offset: 0x00

Reset value: 0x0000 0000

Write only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REVISION[3:0] PARTNO[7:0] Res. Res. Res. MIN

rrrrrrrrrrrr r

1514131211109876543210

VERSION[3:0] DESIGNER[10:0] Res.

rrrrrrrrrrrrrrr

Bits 31:28 REVISION[3:0]: revision code

0x5

Bits 27:20 PARTNO[7:0]: part number for the debug port

0xBA

Bits 19:17 Reserved, must be kept at reset value.

Bit 16 MIN: minimal debug port (MINDP) implementation

0x0: MINDP not implemented (transaction counter and pushed operations are supported)

Bits 15:12 VERSION[3:0]: DP architecture version

0x2: DPv2

Bits 11:1 DESIGNER[10:0]: JEDEC designer identity code

0x23B: Arm

®

JEDEC code

Bit 0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ORUN

ERR

CLR

WD

ERR

CLR

STK

ERR

CLR

STK

CMP

CLR

DAP

ABORT

wwwww

Loading...

Loading...