AES hardware accelerator (AES) RM0453

684/1454 RM0453 Rev 2

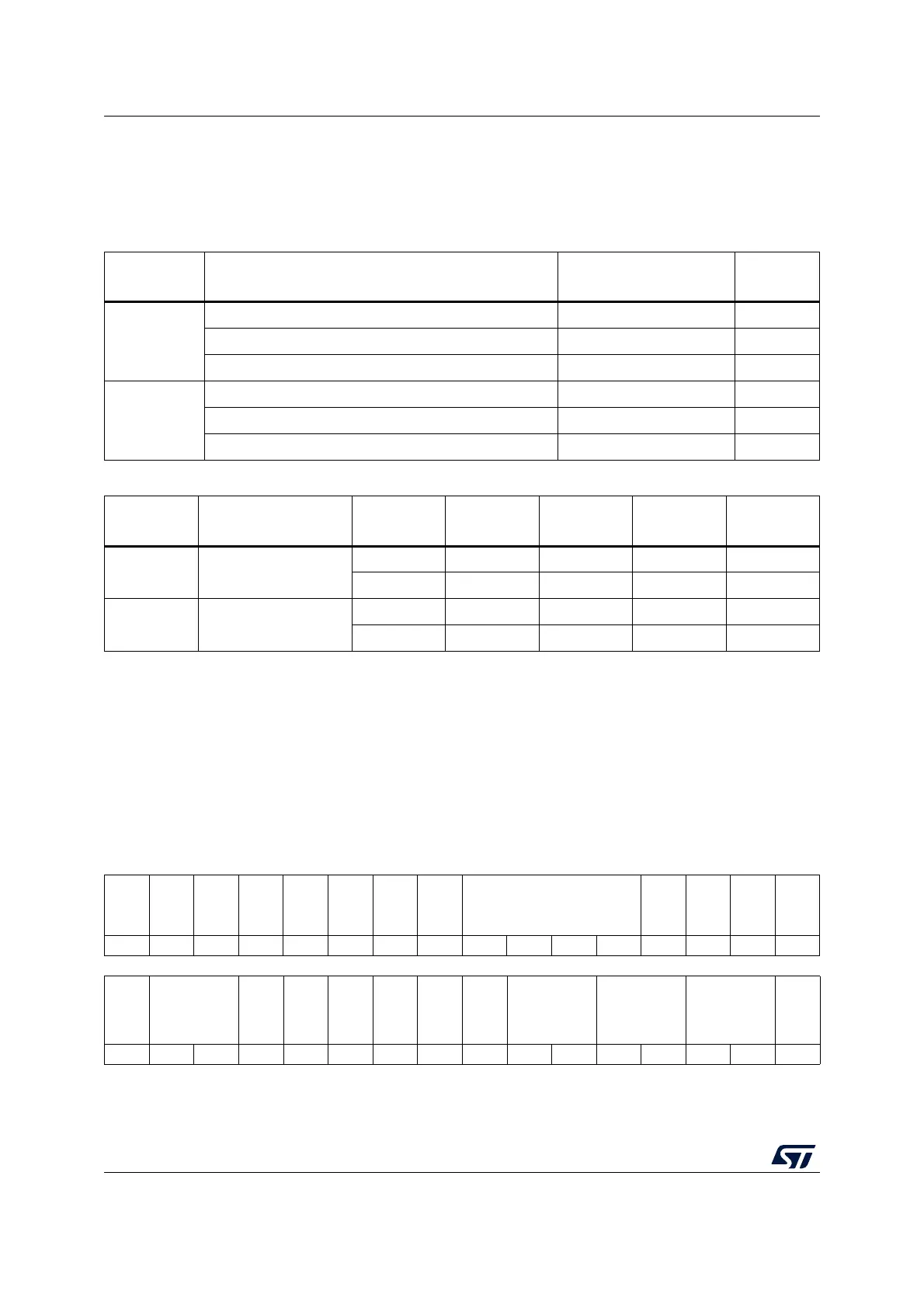

23.6 AES processing latency

The tables below summarize the latency to process a 128-bit block for each mode of

operation.

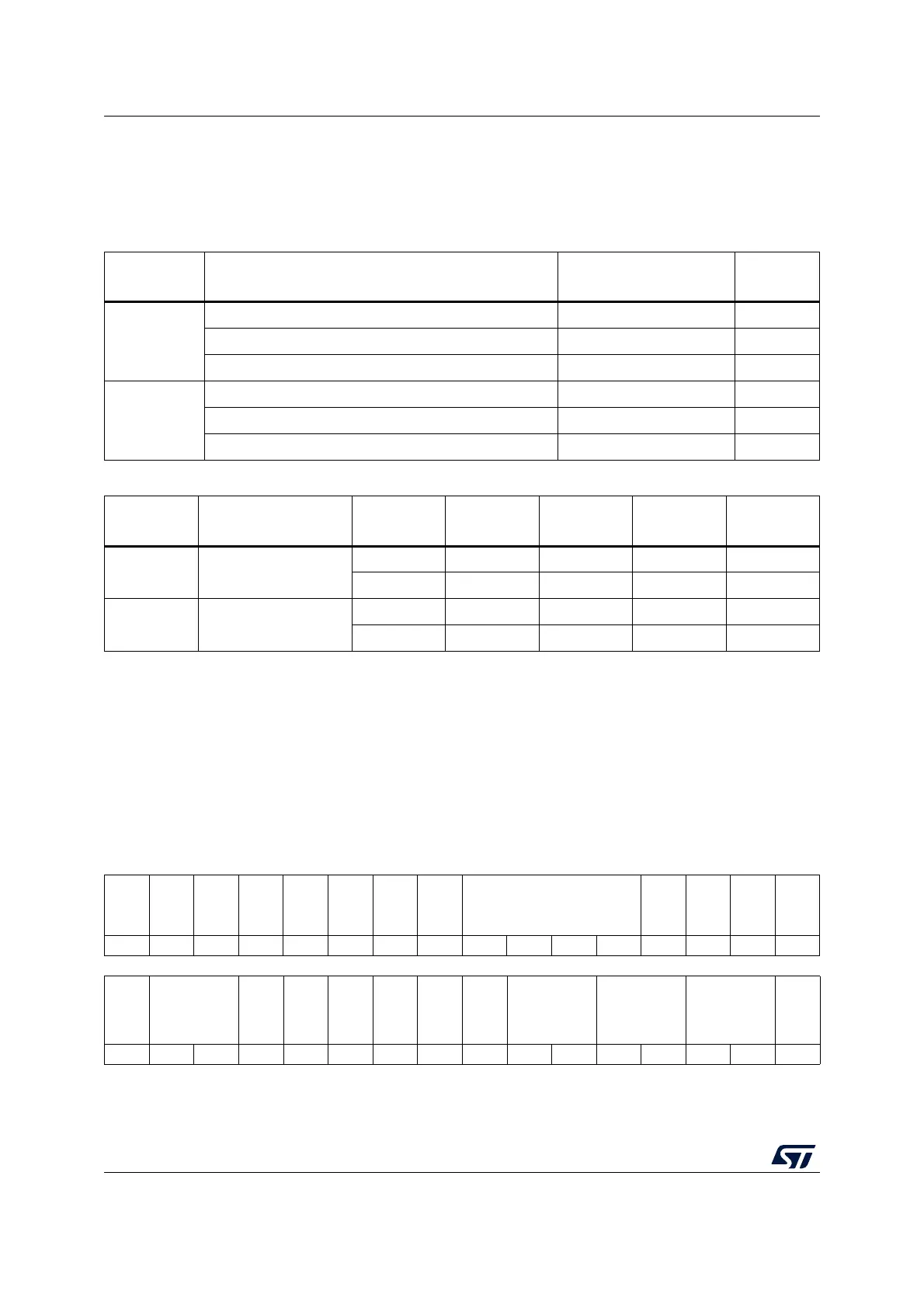

23.7 AES registers

23.7.1 AES control register (AES_CR)

Address offset: 0x00

Reset value: 0x0000 0000

Table 140. Processing latency for ECB, CBC and CTR

Key size Mode of operation Algorithm

Clock

cycles

128-bit

Mode 1: Encryption ECB, CBC, CTR 51

Mode 2: Key derivation - 59

Mode 3: Decryption ECB, CBC, CTR 51

256-bit

Mode 1: Encryption ECB, CBC, CTR 75

Mode 2: Key derivation - 82

Mode 3: Decryption ECB, CBC, CTR 75

Table 141. Processing latency for GCM and CCM (in clock cycles)

Key size Mode of operation Algorithm Init Phase

Header

phase

(1)

Payload

phase

(1)

Tag phase

(1)

128-bit

Mode 1: Encryption/

Mode 3: Decryption

GCM64355159

CCM 63 55 114 58

256-bit

Mode 1: Encryption/

Mode 3: Decryption

GCM88357575

CCM 87 79 162 82

1. Data insertion can include wait states forced by AES on the AHB bus (maximum 3 cycles, typical 1 cycle).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. NPBLB[3:0] Res.

KEYSIZE

Res.

CHMOD[2]

rw rw rw rw rw rw

1514131211109876543210

Res. GCMPH[1:0]

DMAOUTEN

DMAINEN

ERRIE CCFIE ERRC CCFC CHMOD[1:0] MODE[1:0] DATATYPE[1:0] EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Loading...

Loading...