RM0453 Rev 2 967/1454

RM0453 Low-power timer (LPTIM)

973

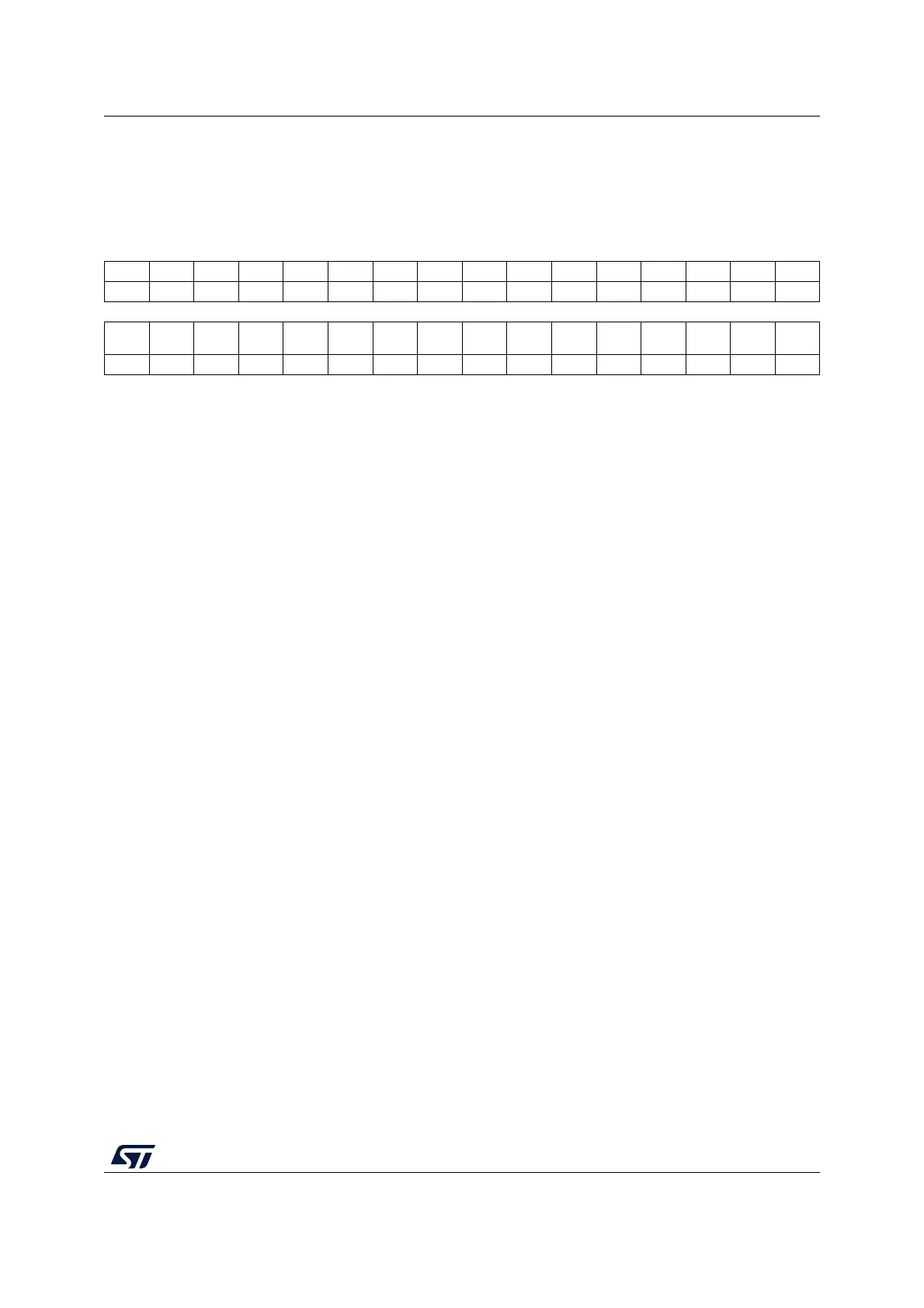

28.7.5 LPTIM control register (LPTIM_CR)

Address offset: 0x010

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

RST

ARE

COUN

TRST

CNT

STRT

SNG

STRT

ENA

BLE

rw rs rw rw rw

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 RSTARE: Reset after read enable

This bit is set and cleared by software. When RSTARE is set to '1', any read access to LPTIM_CNT

register asynchronously resets LPTIM_CNT register content.

This bit can be set only when the LPTIM is enabled.

Bit 3 COUNTRST: Counter reset

This bit is set by software and cleared by hardware. When set to '1' this bit triggers a synchronous

reset of the LPTIM_CNT counter register. Due to the synchronous nature of this reset, it only takes

place after a synchronization delay of 3 LPTimer core clock cycles (LPTimer core clock may be

different from APB clock).

This bit can be set only when the LPTIM is enabled. It is automatically reset by hardware.

Caution: COUNTRST must never be set to '1' by software before it is already cleared to '0' by

hardware. Software should consequently check that COUNTRST bit is already cleared to '0'

before attempting to set it to '1'.

Bit 2 CNTSTRT: Timer start in Continuous mode

This bit is set by software and cleared by hardware.

In case of software start (TRIGEN[1:0] = ‘00’), setting this bit starts the LPTIM in Continuous mode.

If the software start is disabled (TRIGEN[1:0] different than ‘00’), setting this bit starts the timer in

Continuous mode as soon as an external trigger is detected.

If this bit is set when a single pulse mode counting is ongoing, then the timer does not stop at the

next match between the LPTIM_ARR and LPTIM_CNT registers and the LPTIM counter keeps

counting in Continuous mode.

This bit can be set only when the LPTIM is enabled. It is automatically reset by hardware.

Bit 1 SNGSTRT: LPTIM start in Single mode

This bit is set by software and cleared by hardware.

In case of software start (TRIGEN[1:0] = ‘00’), setting this bit starts the LPTIM in single pulse mode.

If the software start is disabled (TRIGEN[1:0] different than ‘00’), setting this bit starts the LPTIM in

single pulse mode as soon as an external trigger is detected.

If this bit is set when the LPTIM is in continuous counting mode, then the LPTIM stops at the

following match between LPTIM_ARR and LPTIM_CNT registers.

This bit can only be set when the LPTIM is enabled. It is automatically reset by hardware.

Bit 0 ENABLE: LPTIM enable

The ENABLE bit is set and cleared by software.

0: LPTIM is disabled.

1: LPTIM is enabled

Loading...

Loading...