176 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 3: Advanced SelectIO Logic Resources

Table 3-15 lists the available ports in the IN_FIFO primitive.

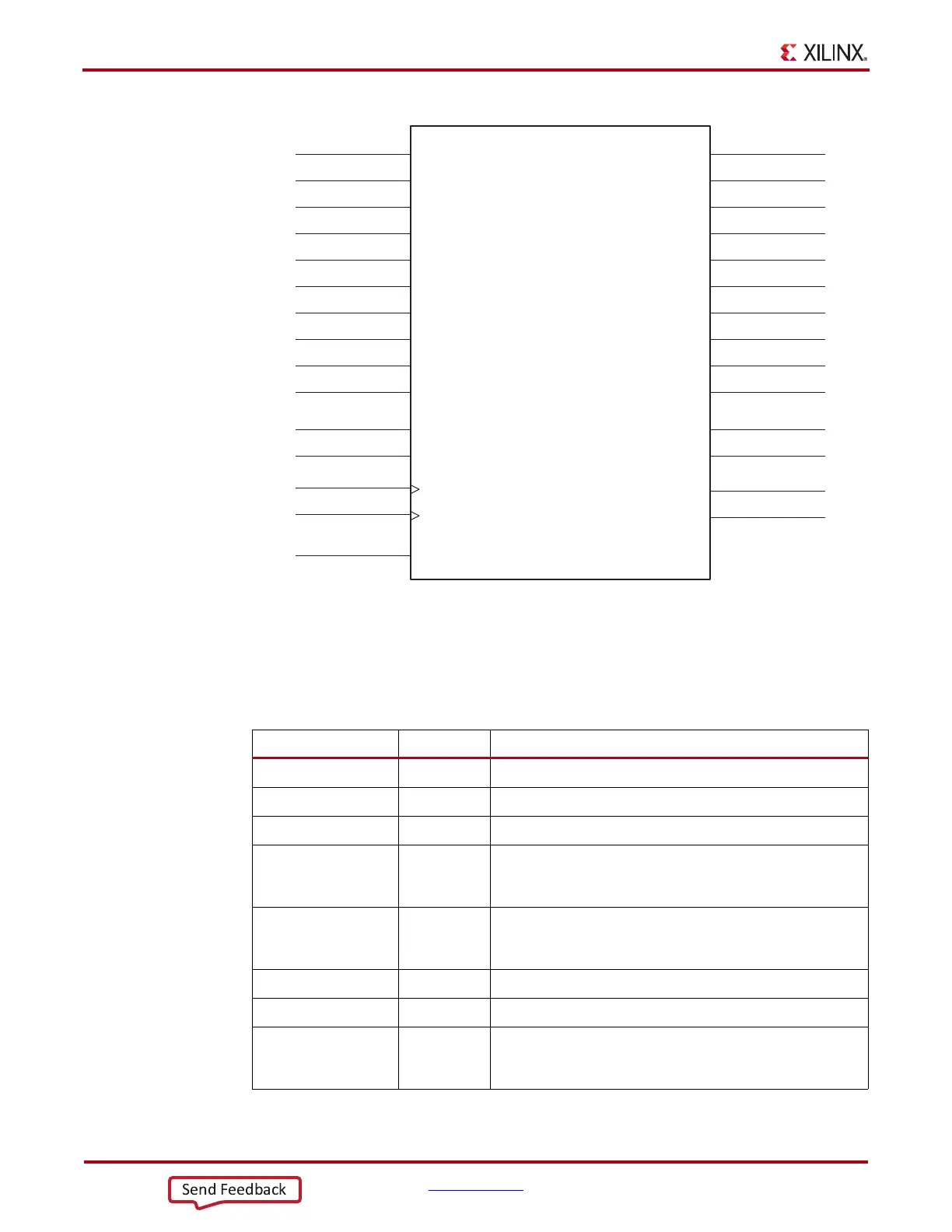

X-Ref Target - Figure 3-20

Figure 3-20: IN_FIFO Primitive

Table 3-15: IN_FIFO Ports

Port Name Input/output Description

RDCLK

I

Read clock. Connect to BUFR, BUFG, or BUFH.

WRCLK

I

Write clock. Connect to BUFR, BUFG, or BUFH.

RESET

I

Reset, active High. Clears all counters, pointers, and data.

D0[3:0] – D9[3:0]

I

Ten 4-bit data in ports in 4 x 8 mode. Twelve 4-bit data in

ports in 4 x 4 mode. Connect to ILOGIC if used for external

interfaces.

D5[7:4], D6[7:4]

I

Supplemental data in ports D10 and D11. Used only in 4 x 4

mode. Data on the ports appears on corresponding output

ports Q5[7:4] and Q6[7:4].

RDEN

I

Read enable.

WREN

I

Write enable.

Q0[7:0] – Q9[7:0]

O

Ten 8-bit data out buses in 4 x 8 mode, or ten 4-bit data out

buses in 4 x 4 mode. Connect to fabric if used for external

interfaces.

D0[3:0]

EMPTY

D1[3:0]

D2[3:0]

D3[3:0]

D4[3:0]

D5[7:0]

D6[7:0]

D7[3:0]

D8[3:0]

D9[3:0]

RDEN

WREN

RDCLK

WRCLK

RESET

Q0[7:0]

Q1[7:0]

Q2[7:0]

Q3[7:0]

Q4[7:0]

Q5[7:0]

Q6[7:0]

Q7[7:0]

Q8[7:0]

Q9[7:0]

FULL

ALMOSTEMPTY

ALMOSTFULL

UG471_c3_20_111611

(1)

(1)

(1)

(1)

Notes:

1. Extra input ports D10 (D5[7:4]) and D11 (D6[7:4]) and output ports Q10 (Q5[7:4]) and

Q11 (Q5[7:4]) in 4 x 4 mode.

Loading...

Loading...