42 Chapter 2

E4438C Vector Signal Generator Overview

Rear Panel Overview

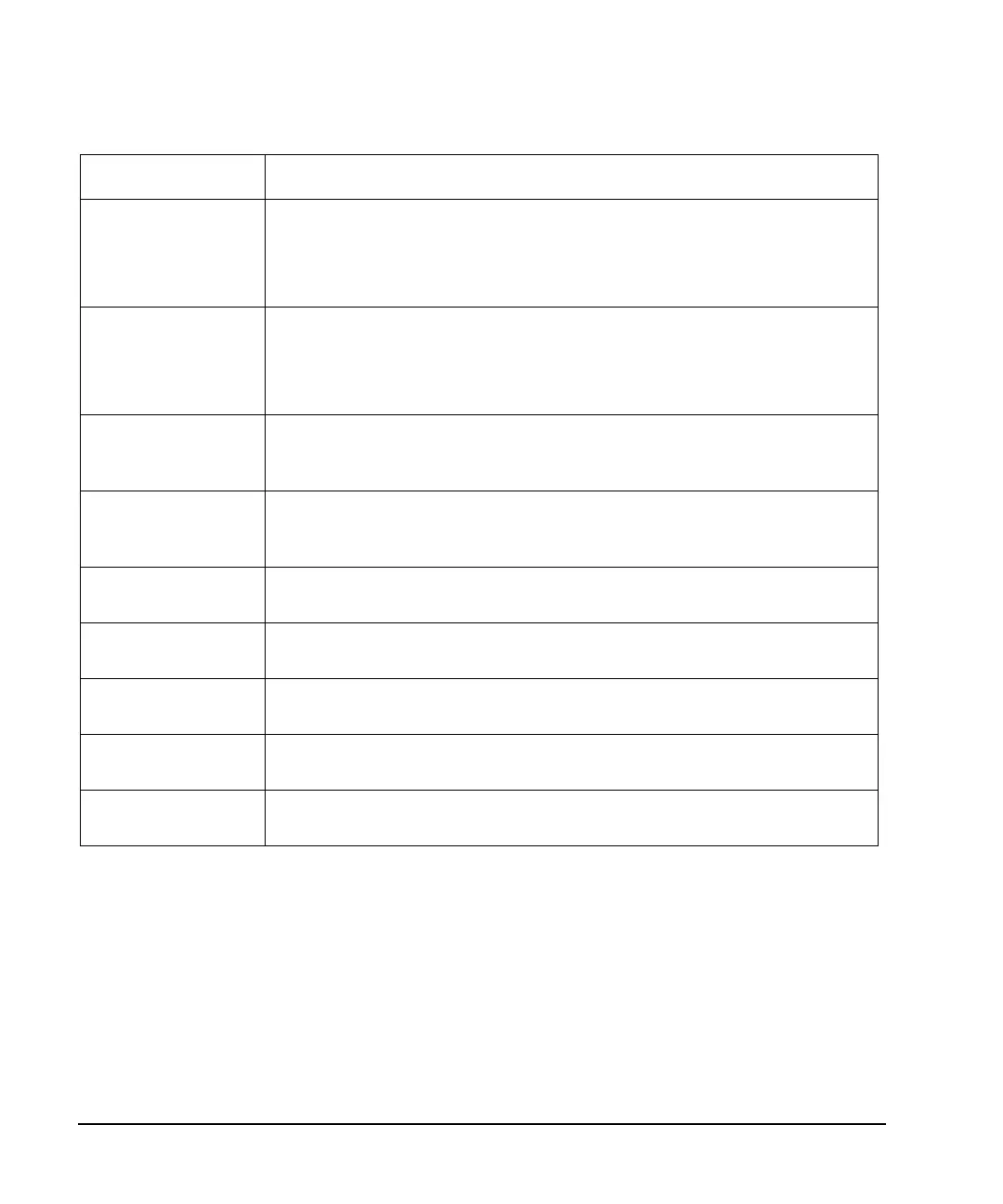

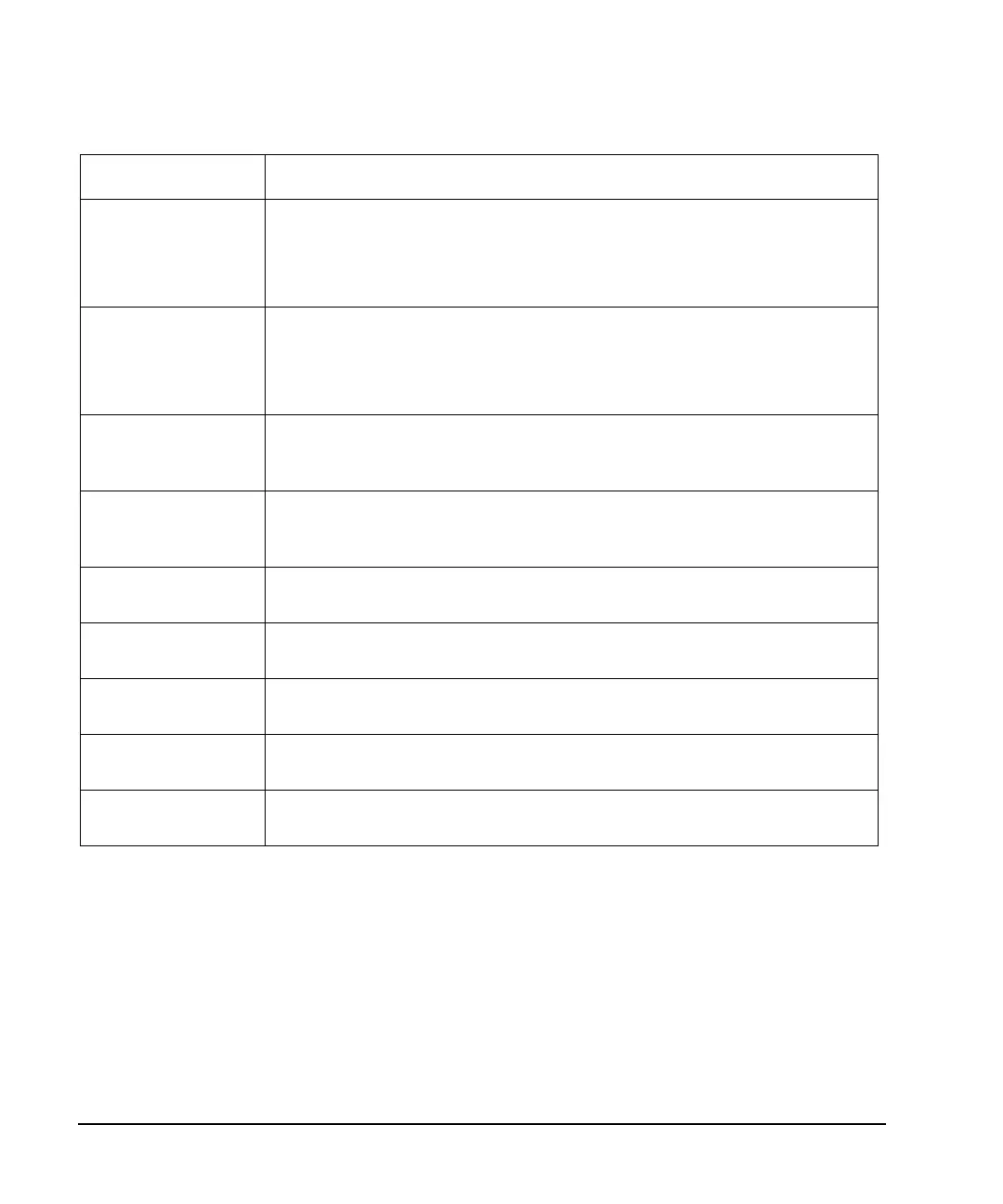

EVENT 3 Pin-19 of the Aux I/O connector is used with an internal baseband generator. In arbitrary

waveform mode, this pin outputs a timing signal generated by Marker 3.

The marker 3 output level is +3.3 V CMOS regardless of marker polarity settings.The

reverse damage levels for this connector pin are > +5.5 volts and < −0.5 volts.

EVENT 4 Pin-18 of the Aux I/O connector is used with an internal baseband generator. In arbitrary

waveform mode, this pin outputs a timing signal generated by Marker 4.

The marker 4 output level is +3.3 V CMOS regardless of marker polarity settings. The

reverse damage levels for this connector pin are > +5.5 volts and < −0.5 volts.

PATT TRIG IN 2 Pin-17 of the Aux I/O connector accepts a signal that triggers an internal pattern or frame

generator to start single pattern output. Minimum pulse width is 100 ns. Damage levels

are > +5.5 and < −0.5 V.

SYM SYNC OUT Pin-5 of the Aux I/O connector is used with an internal baseband generator. This pin

outputs the CMOS symbol clock for symbol synchronization, one data clock period

wide. Damage levels are > +5.5 volts and < −0.5 volts.

BER MEAS TRIG/BER

NO DATA

Pin-22 is used for bit error rate testing (Option UN7). Damage levels are > +5.5 volts

and < −0.5 volts.

BER ERR OUT Pin-21 is used for bit error rate testing (Option UN7). Damage levels are > +5.5 volts

and < −0.5 volts

BER TEST OUT Pin-20 is used for bit error rate testing (Option UN7). Damage levels are > +5.5 volts

and < −0.5 volts

BER SYNC LOSS Pin-4 is used for bit error rate testing (Option UN7). Damage levels are > +5.5 volts and

< −0.5 volts.

BER MEAS END Pin-1 is used for bit error rate testing (Option UN7). Damage levels are > +5.5 volts and

< −0.5 volts.

Connector Pin

Description

(Continued)

Loading...

Loading...