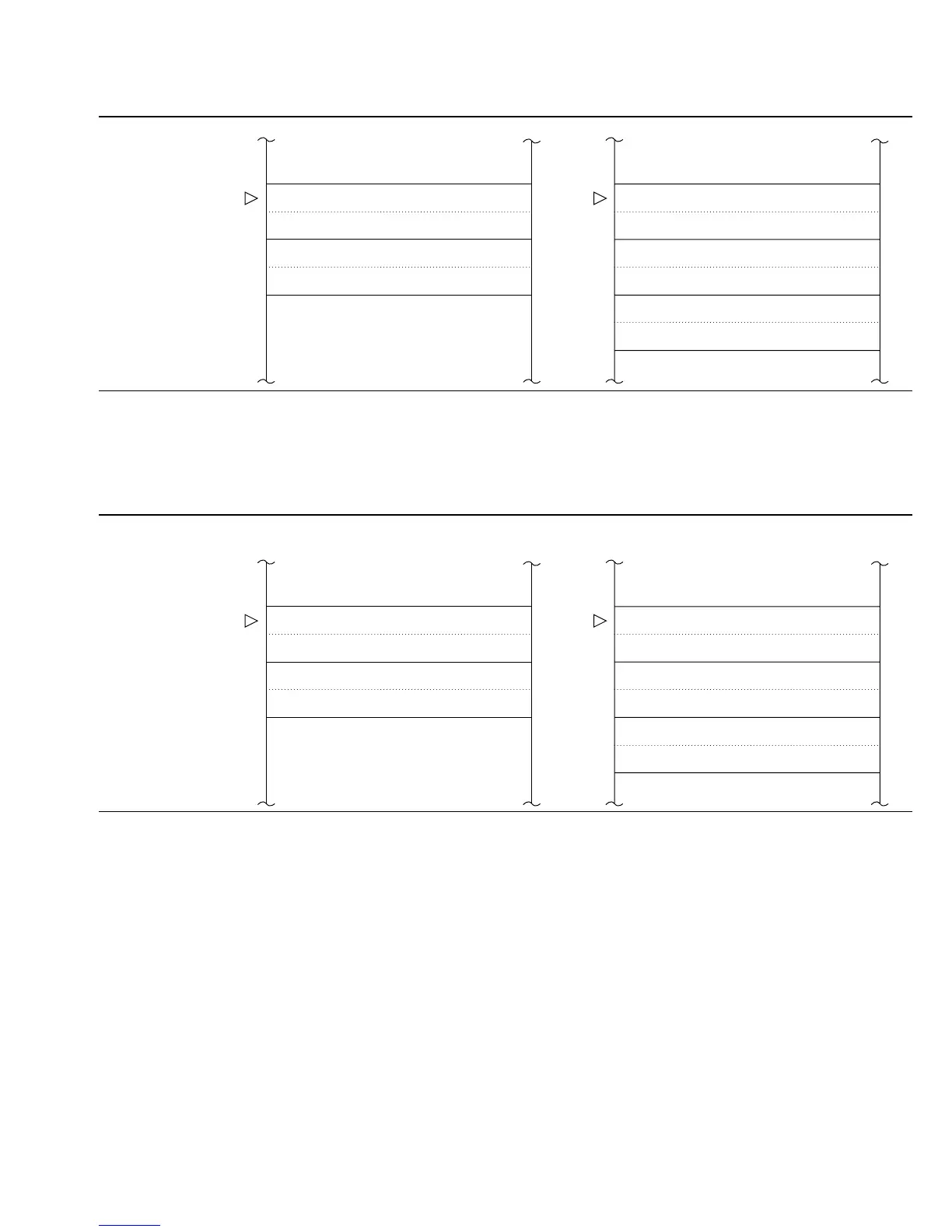

Table 4-3 Stack after Exception Handling Sequence (cont)

Note: The program counter value pushed on the stack is not necessarily the address of the first

byte of the invalid instruction.

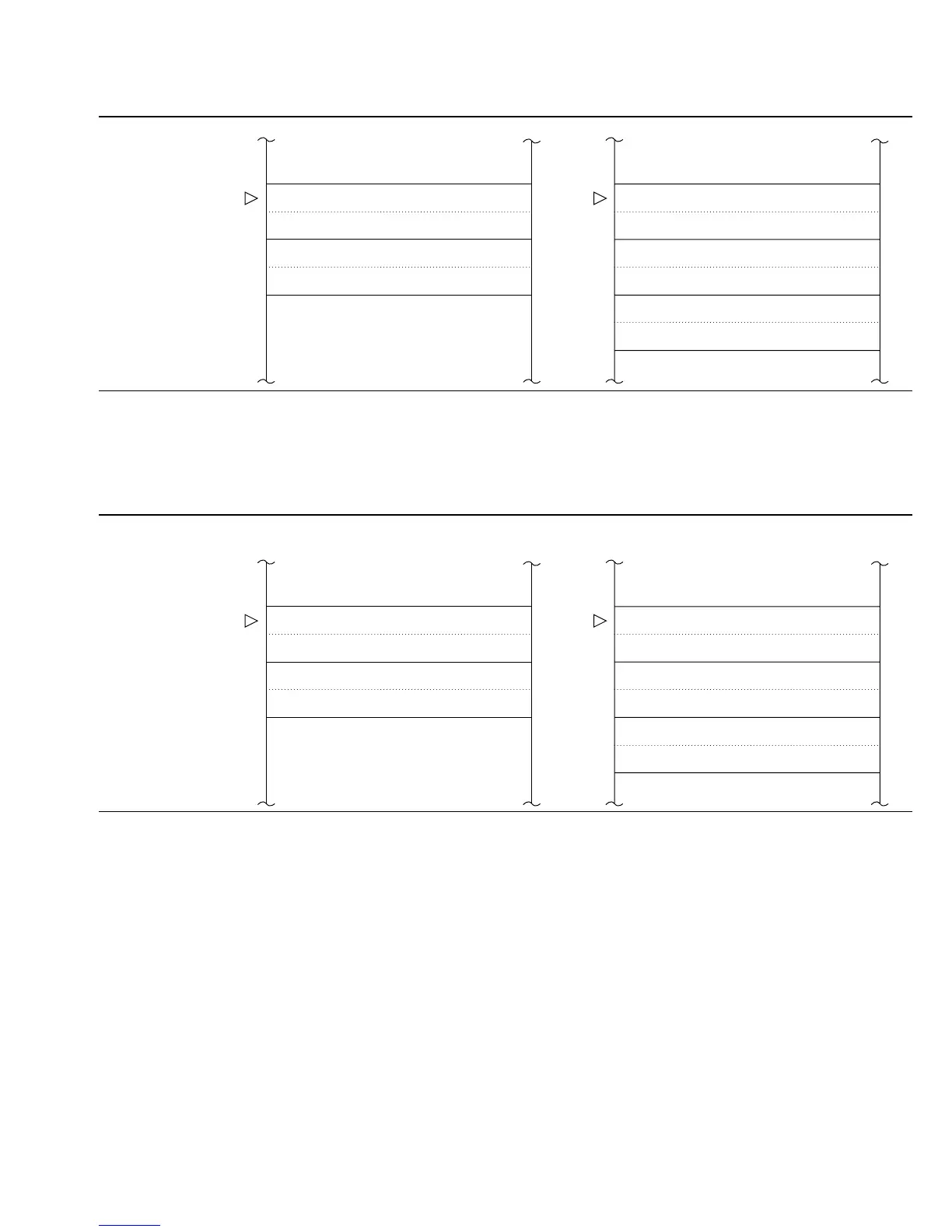

Note: The program counter value pushed on the stack is the address of the next instruction after

the last instruction successfully executed.

Exception Factor Minimum Mode Maximum Mode

Invalid

instruction

SP SR (upper byte) TP:SP SR (upper byte)

SR (lower byte) SR (lower byte)

PC when error occurred (upper byte) Don’t-care

PC when error occurred (lower byte) CP when error occurred (8 bits)

PC when error occurred (upper byte)

PC when error occurred (lower byte)

Address

error

SP SR (upper byte) TP:SP SR (upper byte)

SR (lower byte) SR (lower byte)

PC when error occurred (upper byte) Don’t-care

PC when error occurred (lower byte) CP when error occurred (8 bits)

PC when error occurred (upper byte)

PC when error occurred (lower byte)

95

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...