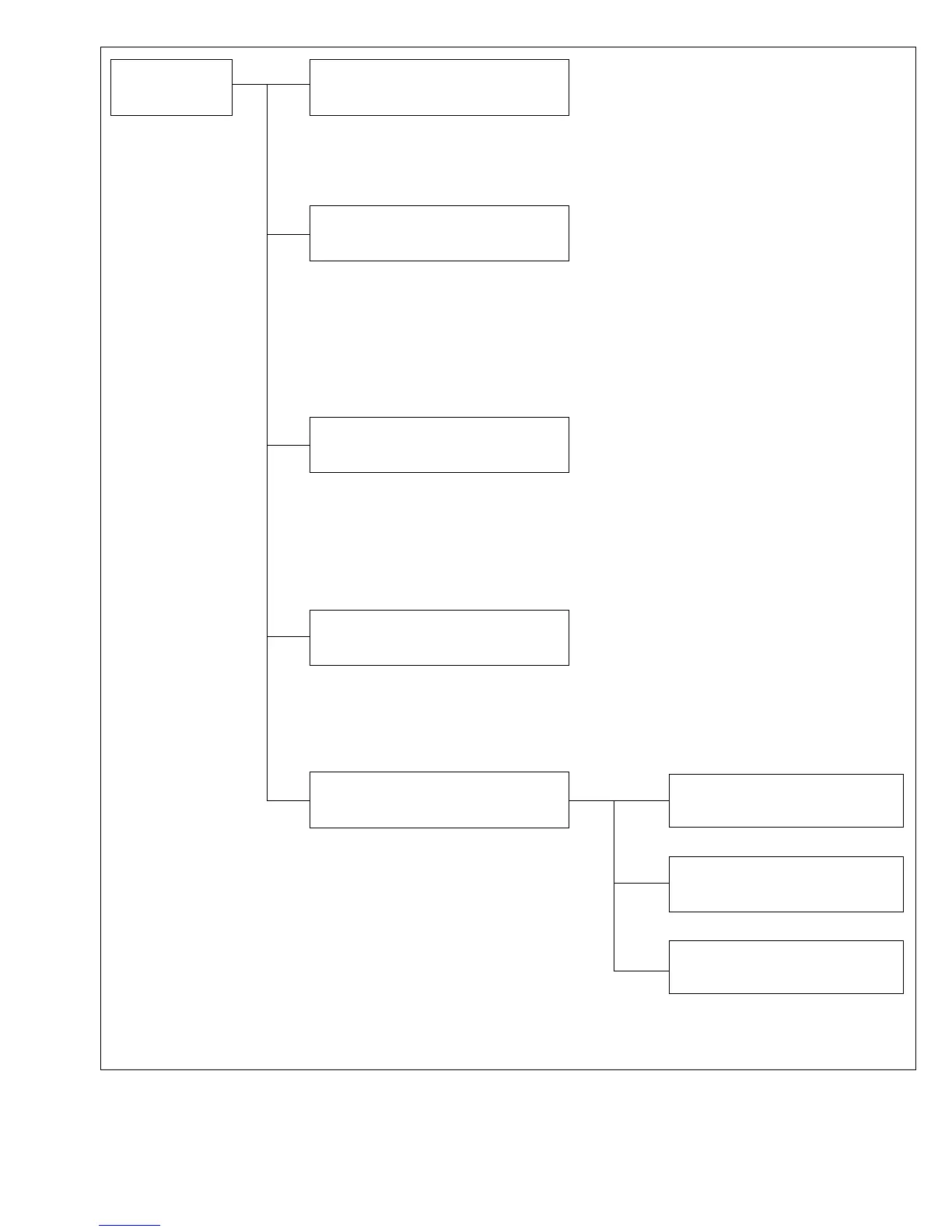

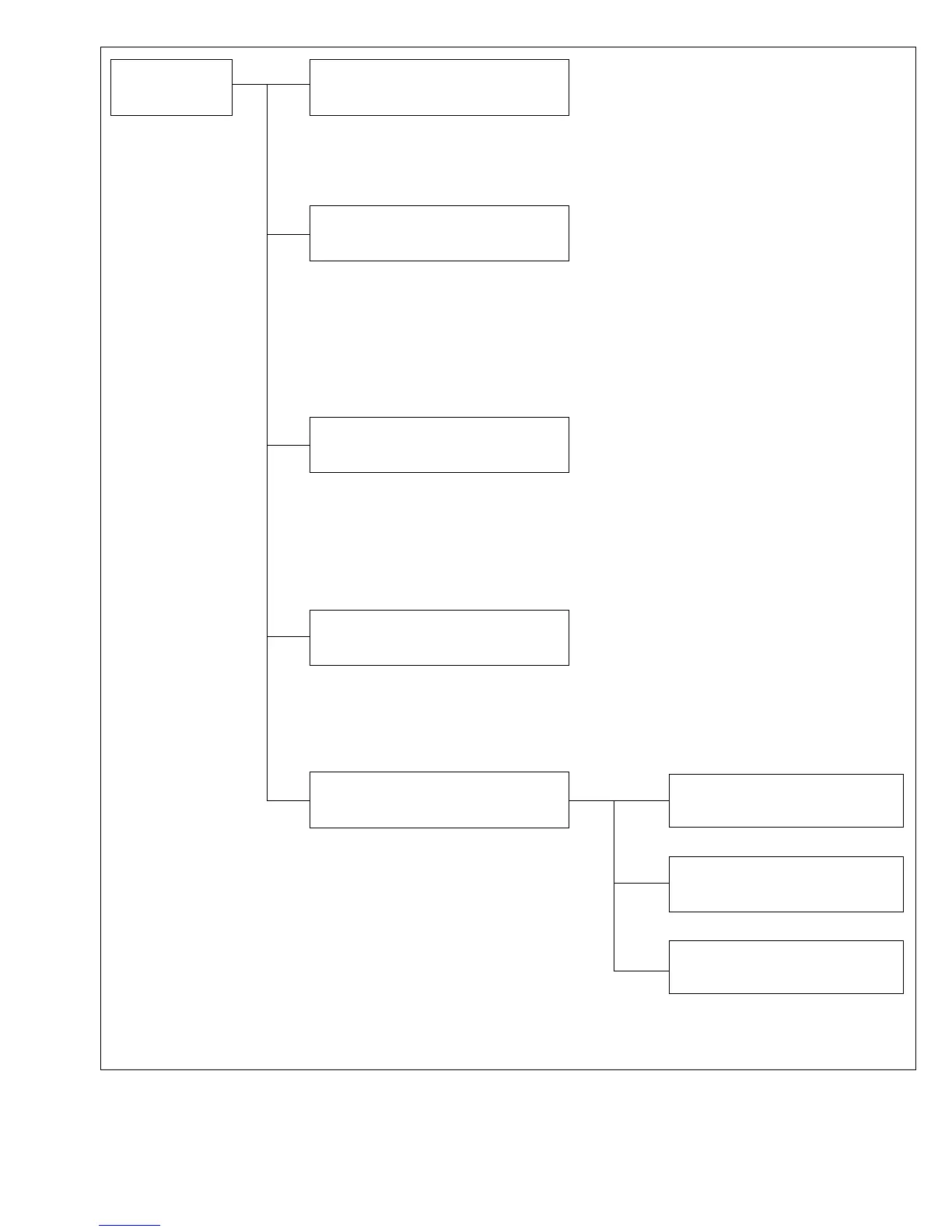

State Program execution state

Exception-handling state

Bus-released state

Reset state

Power-down state

The CPU executes program instructions in sequence.

A transient state in which the CPU executes a hardware

sequence (saving the program counter and status register,

fetching a vector from the vector table, etc.) triggered by a reset,

interrupt, or other exception.

The state in which the CPU has released the external bus in

response to a bus request signal from an external device, and

is waiting for the bus to be returned.

The state in which the CPU and all on-chip supporting

modules have been initialized and are stopped.

A state in which some

or all of the clock

signals are stopped to

conserve power.

Sleep mode

Software standby mode

Hardware standby mode

Figure 3-11 Operating States

70

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...