14.2.5 Serial Mode Register (SMR)—H'FFD8

The SMR is an 8-bit readable/writable register that controls the communication format and selects

the clock rate for the internal clock source. It is initialized to H'04 at a reset and in the standby

modes.

Bit 7—Communication Mode (C/A): This bit selects the asynchronous or synchronous

communication mode.

Bit 7

C/A Description

0 Asynchronous communication. (Initial value)

1 Communication is synchronized with the serial clock.

Bit 6—Character Length (CHR): This bit selects the character length in asynchronous mode. It

is ignored in synchronous mode.

Bit 6

CHR Description

0 8 Bits per character. (Initial value)

1 7 Bits per character.

Bit 5—Parity Enable (PE): This bit selects whether to add a parity bit in asynchronous mode. It

is ignored in synchronous mode.

Bit 5

PE Description

0 Transmit: No parity bit is added. (Initial value)

Receive: Parity is not checked.

1 Transmit: A parity bit is added.

Receive: Parity is not checked.

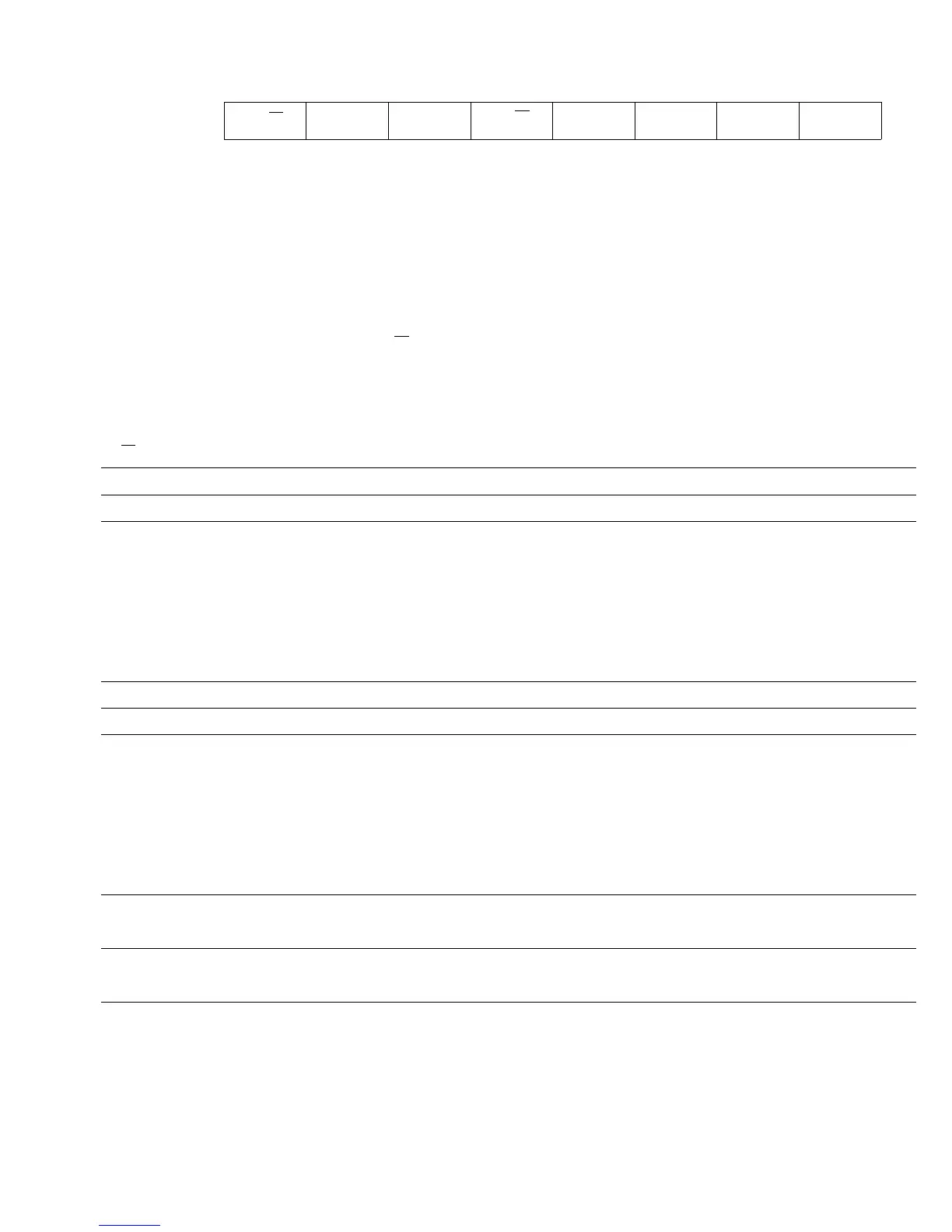

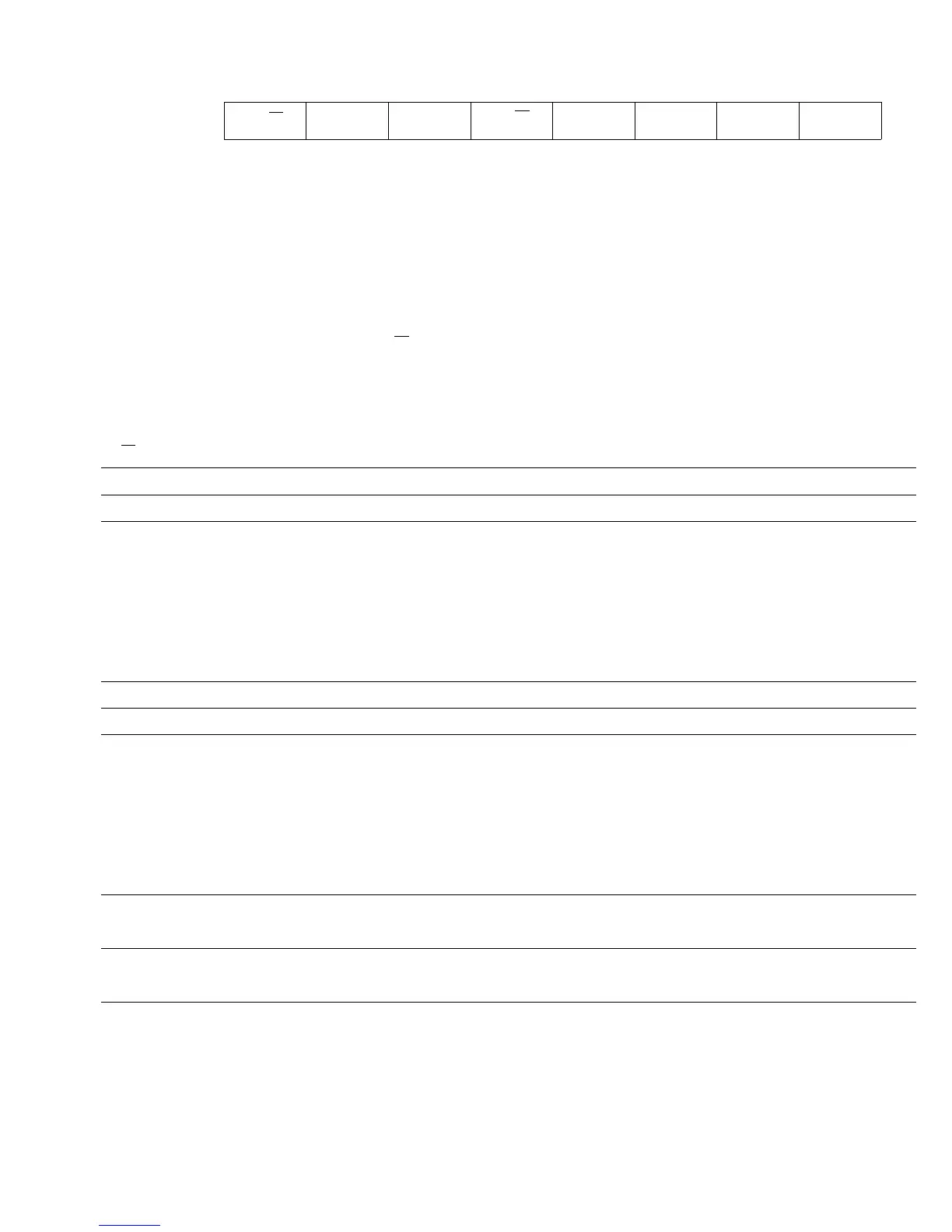

Bit 76543210

C/A CHR PE O/E STOP — CKS1 CKS0

Initial value 00000100

Read/Write R/W R/W R/W R/W R/W — R/W R/W

249

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...