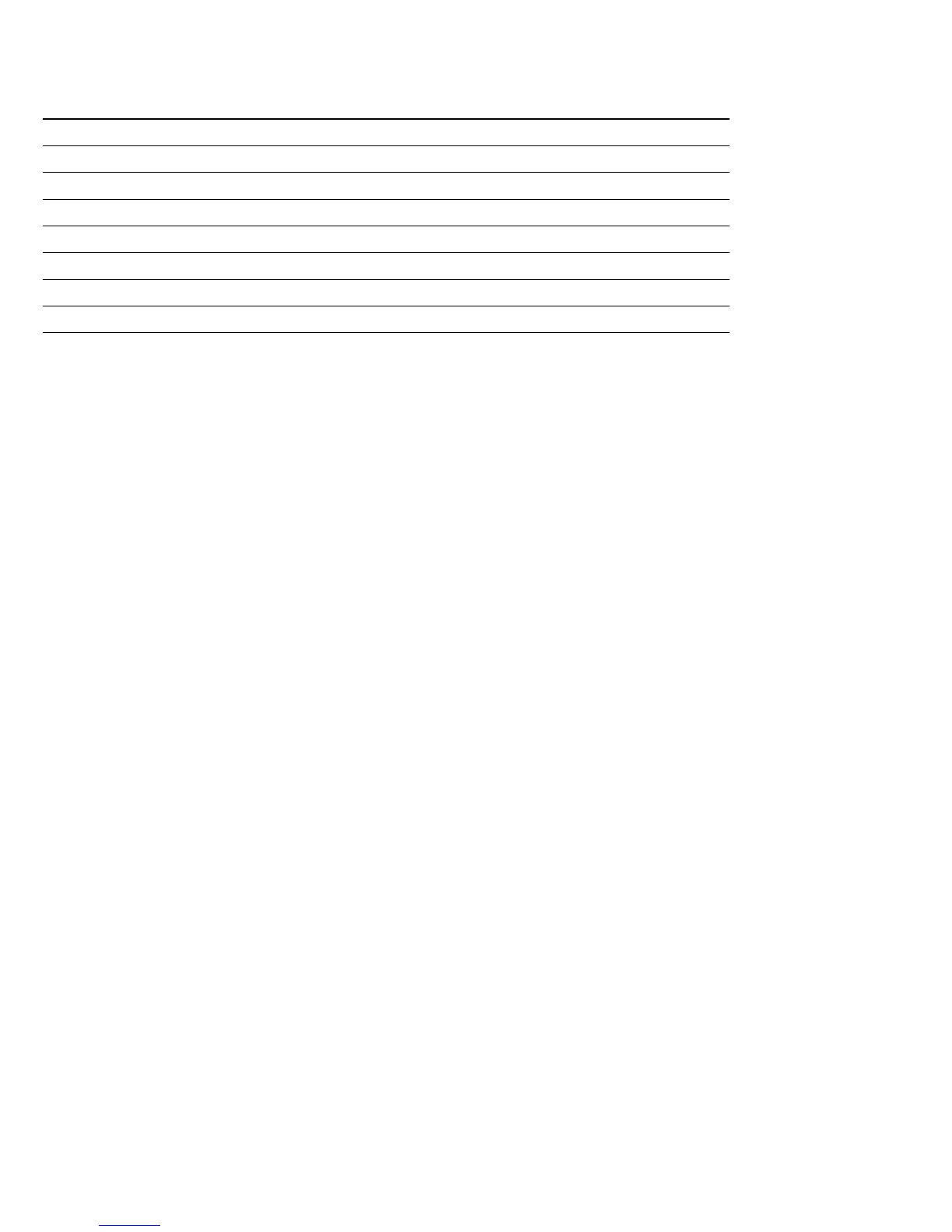

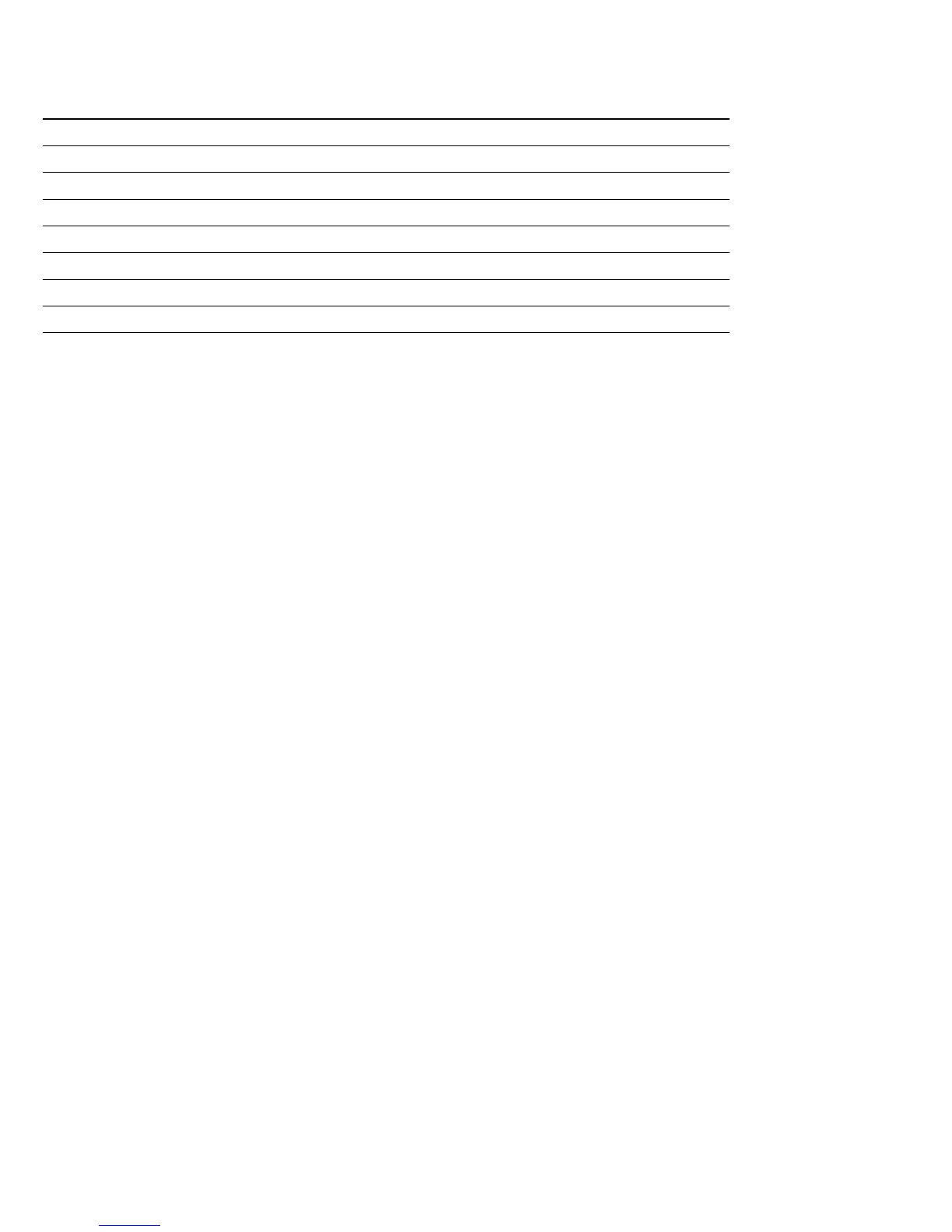

Table 12-3 PWM Timer Parameters for 10MHz System Clock

12.3 Operation

Figure 12-2 shows the timing of the PWM timer operation.

1. Positive Logic (OS = “0”)

(1) When OE = “0”—(a) in figure 12-2: The timer count is held at H'00 and PWM output is

inhibited. (The pin is used for port 9 input/output, and its state depends on the corresponding

port 9 data register and data direction register.) Any value (such as N in figure 12-2) written

in the DTR becomes valid immediately.

(2) When OE = “1”

i) The timer counter begins incrementing, and the PWM output goes High. [(b) in figure 12-2]

ii) When the count reaches the DTR value, the PWM output goes Low. [(c) in figure 12-2]

iii)If the DTR value is changed (by writing the data “M” in figure 12-2), the new value

becomes valid after the timer count changes from H'F9 to H'00. [(d) in figure 12-2]

2. Negative Logic (OS = “1”): The operation is the same except that High and Low are reversed

in the PWM output. [(e) in figure 12-2]

Internal Clock Frequency Resolution PWM Period PWM Frequency

ø/2 200ns 50µs 20kHz

ø/8 800ns 200µs 5kHz

ø/32 3.2µs 800µs 1.25kHz

ø/128 12.8µs 3.2ms 312.5Hz

ø/256 25.6µs 6.4ms 156.3Hz

ø/1024 102.4µs 25.6ms 39.1Hz

ø/2048 204.8µs 51.2ms 19.5Hz

ø/4096 409.6µs 102.4ms 9.8Hz

232

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...