M = {(0.5 – 1/2N) – (D – 0.5)/N – (L – 0.5)F} × 100 [%] (1)

N: Receive margin

N: Ratio of basic clock to bit rate (16)

D: Duty factor of clock—ratio of High pulse width to Low width (0.5 to 1.0)

L: Frame length (9 to 12)

F: Absolute clock frequency deviation

When D = 0.5 and F= 0

M = (0.5 –1/2 × 16) × 100 [%] = 46.875% (2)

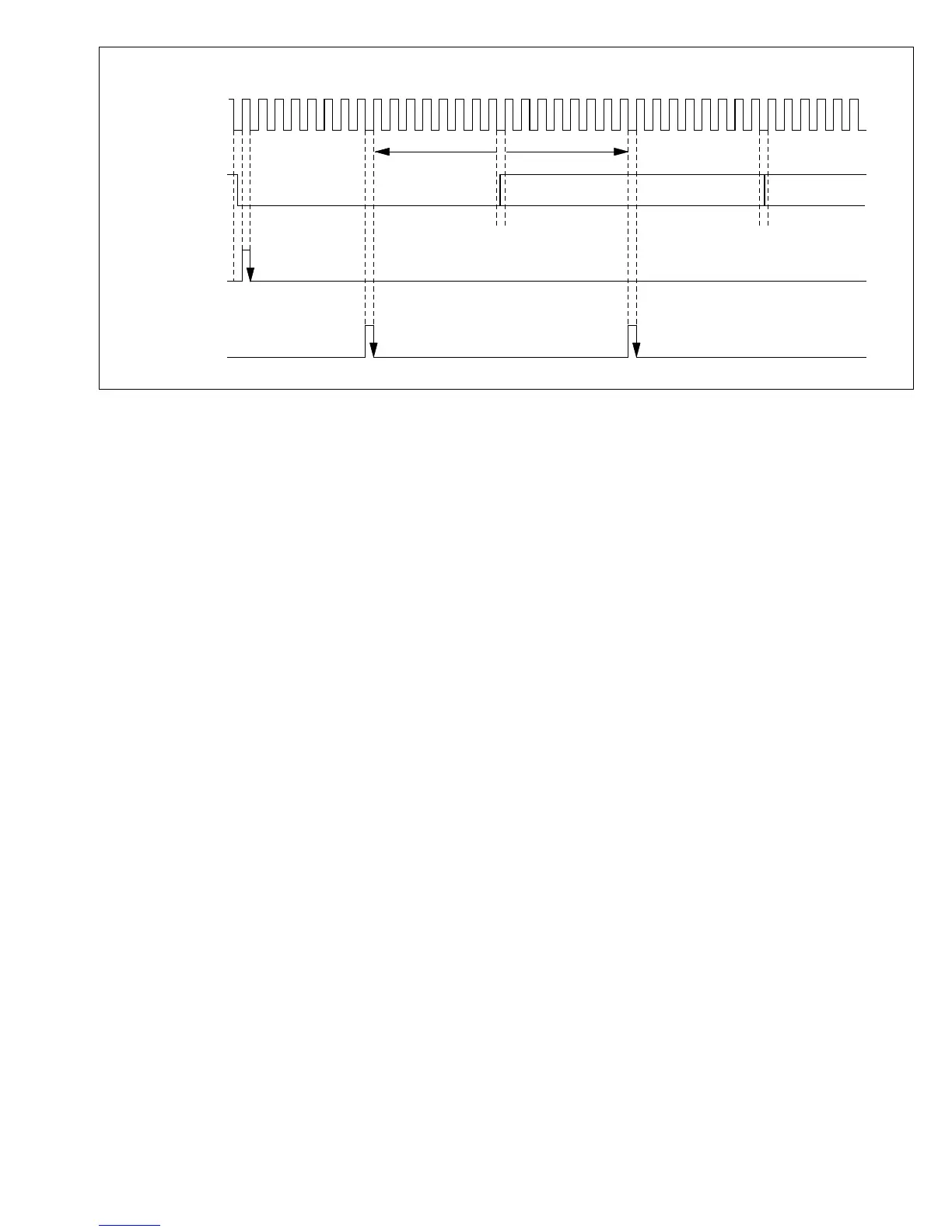

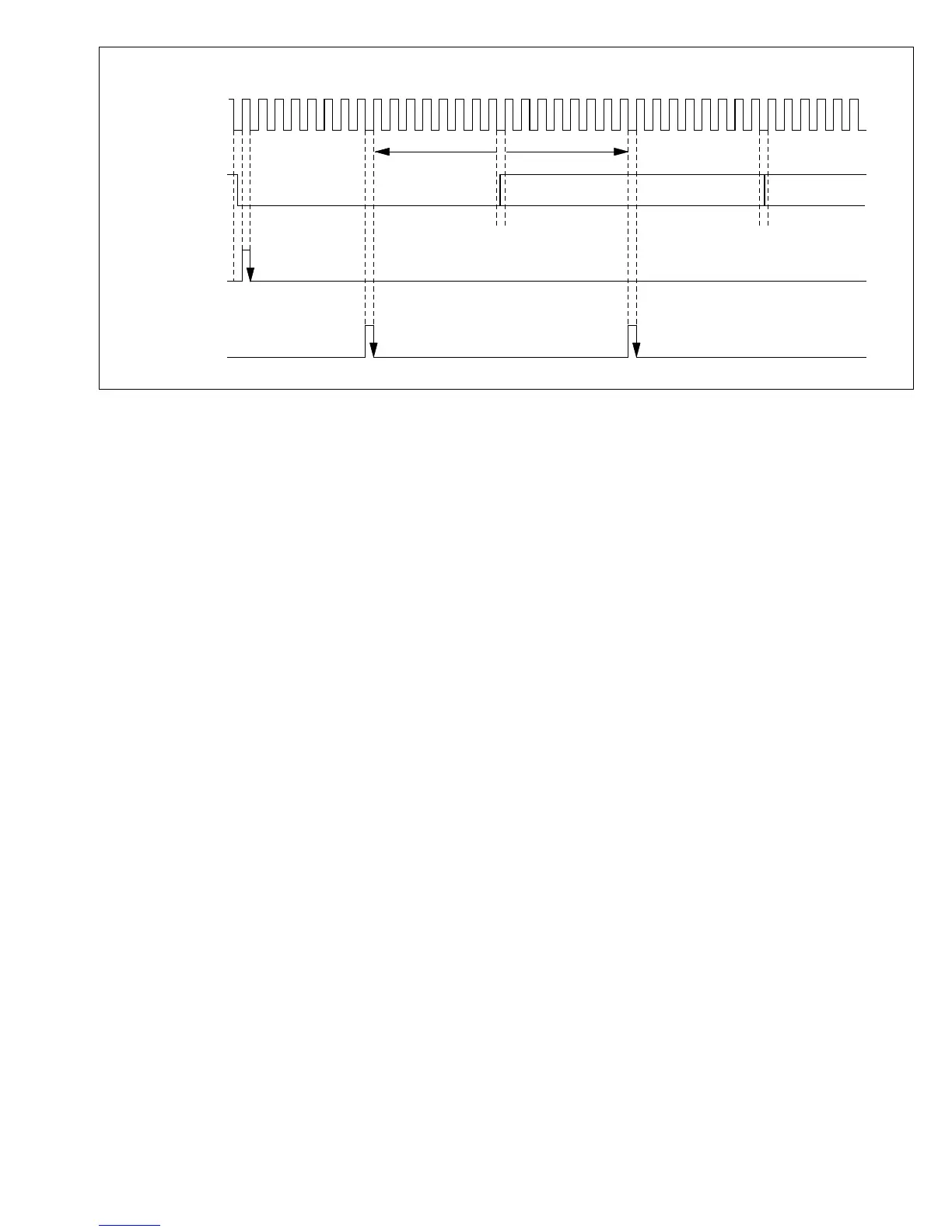

Basic clock

Receive data

Start bit

Sync sampling

Data sampling

–7.5 pulses +7.5 pulses

D0 D1

0123456789101112131415161234567891011121314151612345

Figure 14-5 Sampling Timing (Asynchronous Mode)

271

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...