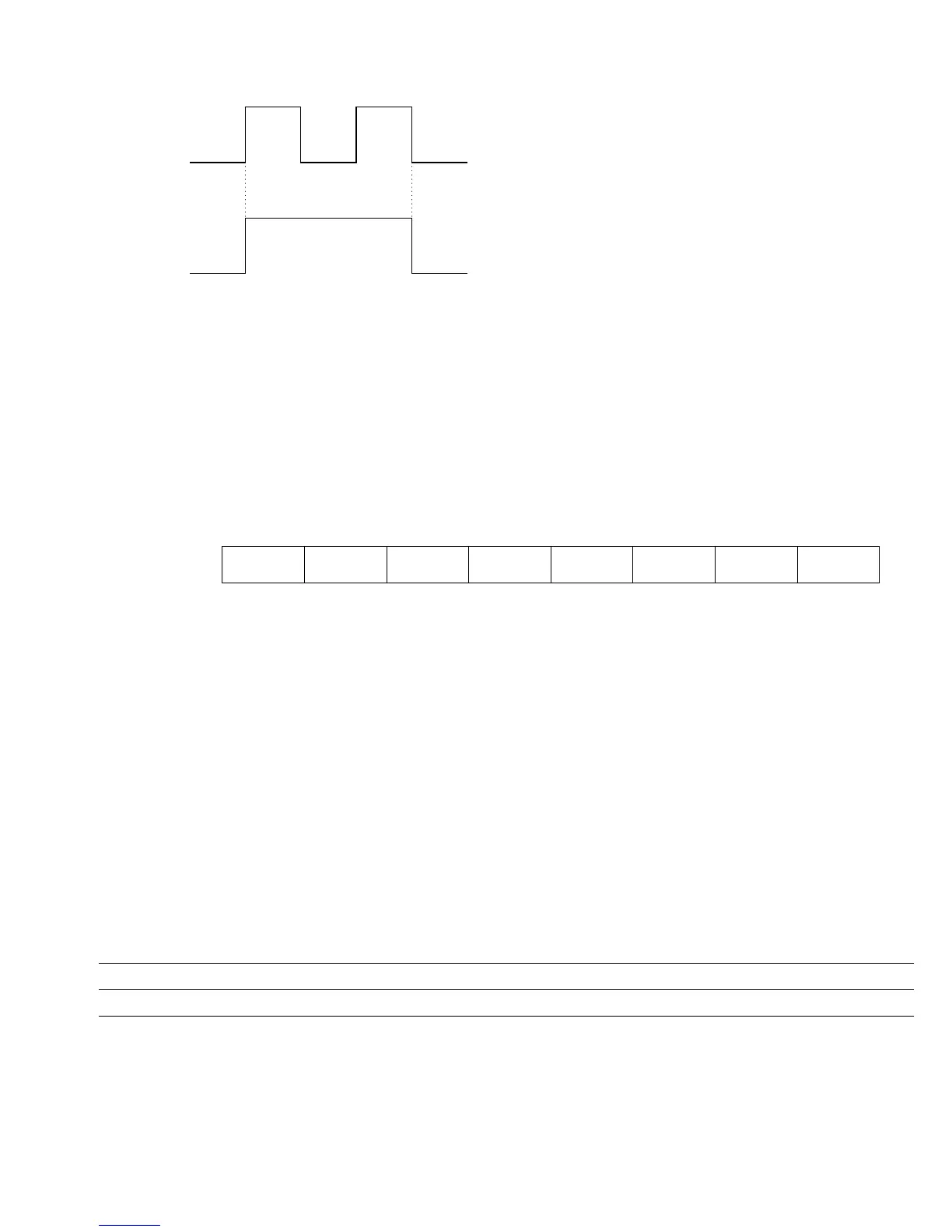

To ensure input capture, the pulse width of the input capture signal should be at least 1.5 system

clock periods (1.5·ø).

The ICR is initialized to H'0000 at a reset and in the standby modes.

Note: When input capture is detected, the FRC value is transferred to the ICR even if the input

capture flag (ICF) is already set.

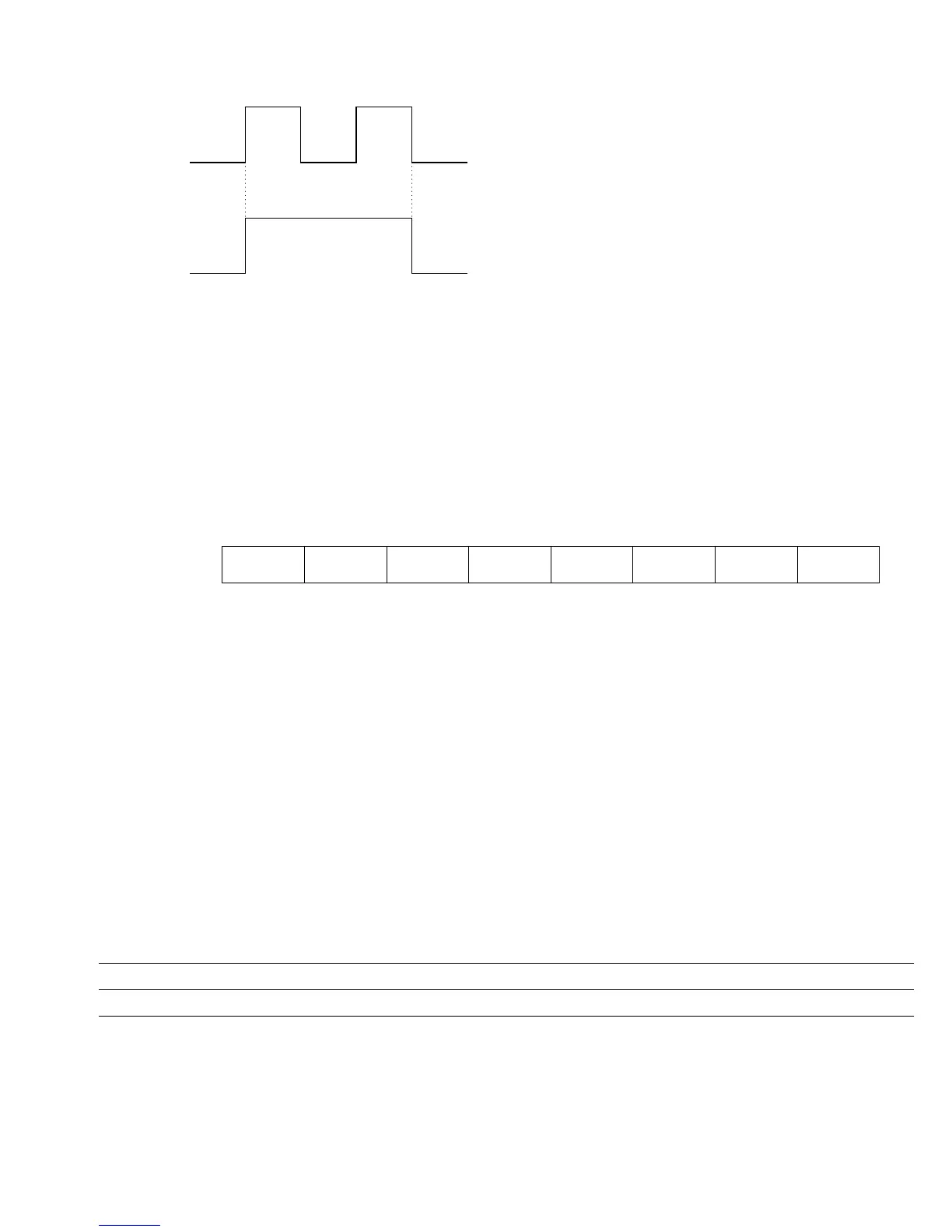

10.2.4 Timer Control Register (TCR)

The TCR is an 8-bit readable/writable register that selects the FRC clock source, enables the

output compare signals, and enables interrupts.

The TCR is initialized to H'00 at a reset and in the standby modes.

Bit 7—Input Capture Interrupt Enable (ICIE): This bit selects whether to request an input

capture interrupt (ICI) when the input capture flag (ICF) in the timer status/control register

(TCSR) is set to “1.”

Bit 7

ICIE Description

0 The input capture interrupt request (ICI) is disabled. (Initial value)

1 The input capture interrupt request (ICI) is enabled.

Bit 6—Output Compare Interrupt Enable B (OCIEB): This bit selects whether to request

output compare interrupt B (OCIB) when output compare flag B (OCFB) in the timer

status/control register (TCSR) is set to “1.”

ø

FTI

Minimum FTI Pulse Width

Bit 76543210

ICIE OCIEB OCIEA OVIE OEB OEA CKS1 CKS0

Initial value 00000000

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

183

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...