A.4 Instruction Execution Cycles

Tables A-7 (1) through (6) list the number of cycles required by the CPU to execute each

instruction in each addressing mode.

The meaning of the symbols in the tables is explained below. The values of I, J, and K are used to

calculate the number of execution cycles when off-chip memory is accessed for an instruction

fetch or operand read/write. The formulas for these calculations are given next.

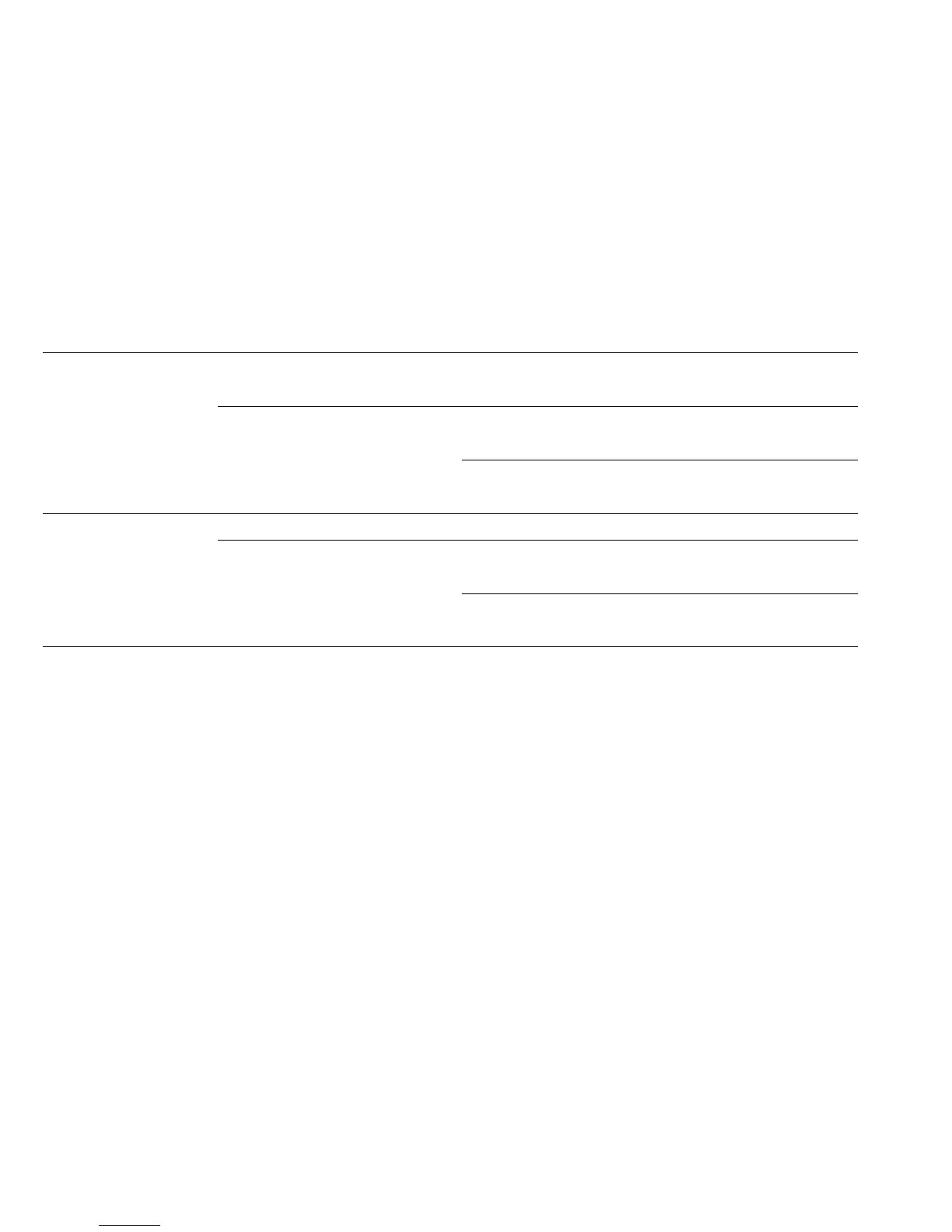

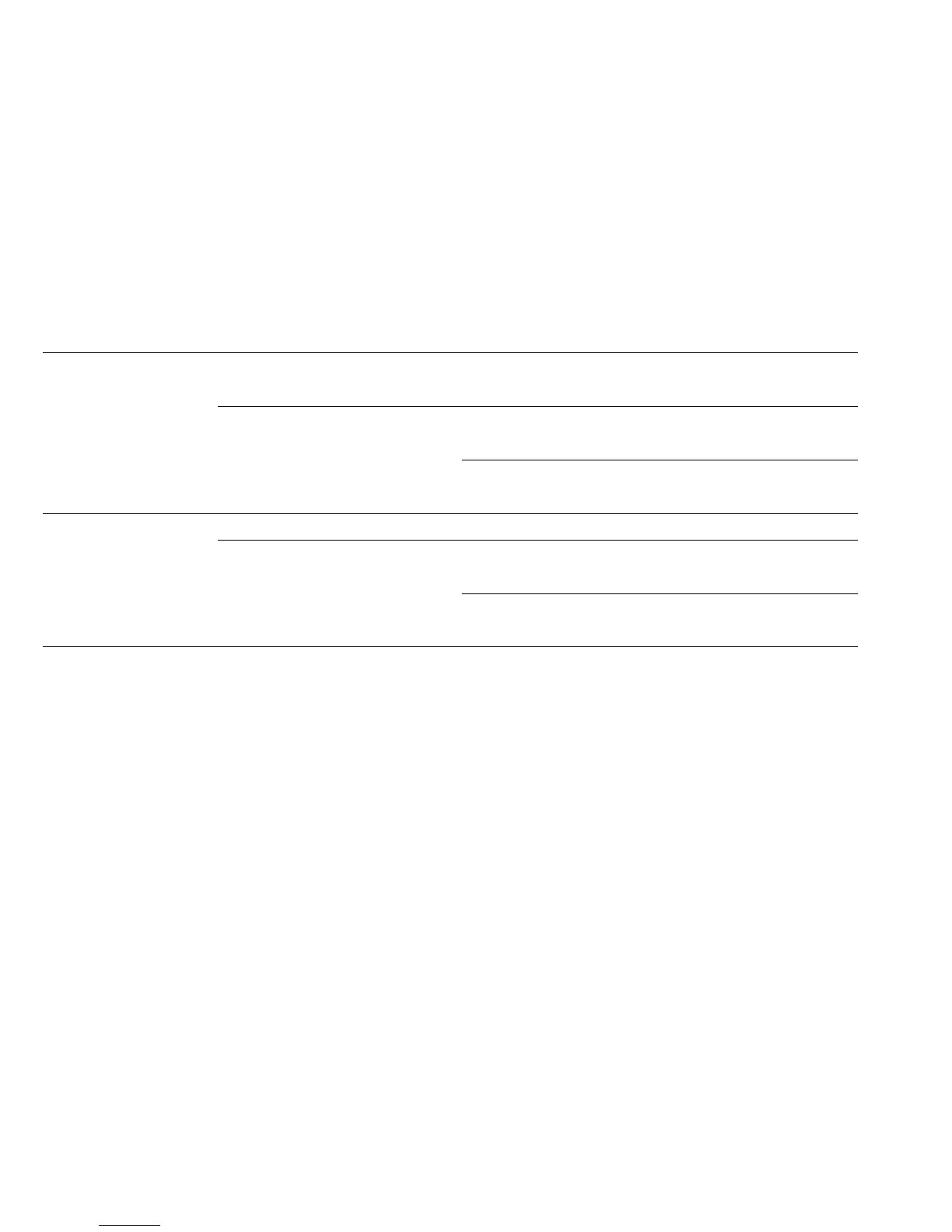

A.4.1 Calculation of Instruction Execution States

Instruction Fetch Operand Read/Write Number of States

On-chip memory On-chip memory (Value given in table A-7) +

(Value in table A-8)

On-chip memory module Byte (Value in table A-7) +

or off-chip memory (Value in table A-8) + I

Word ((Value in table A-7) +

(Value in table A-8) + 2I

Off-chip memory On-chip memory (Value given in table A-7) + 2(J + K)

On-chip supporting module Byte (Value in table A-7) +

or off-chip memory I + 2(J + K)

Word ((Value in table A-7) +

2(I + J + K)

Notes: *1. When the instruction is fetched from on-chip memory (ROM or RAM), the number of

execution states varies by 1 or 2 depending of whether the instruction is stored at an

even or odd address. This difference must be noted when software is used for timing,

and in other cases in which the exact number of states is important.

*2. If wait states are inserted in access to external memory, add the necessary number of

cycles.

*1

*2

*2

*2

358

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...