5.3 Register Descriptions

5.3.1 Interrupt Priority Registers A to D (IPRA to IPRD)

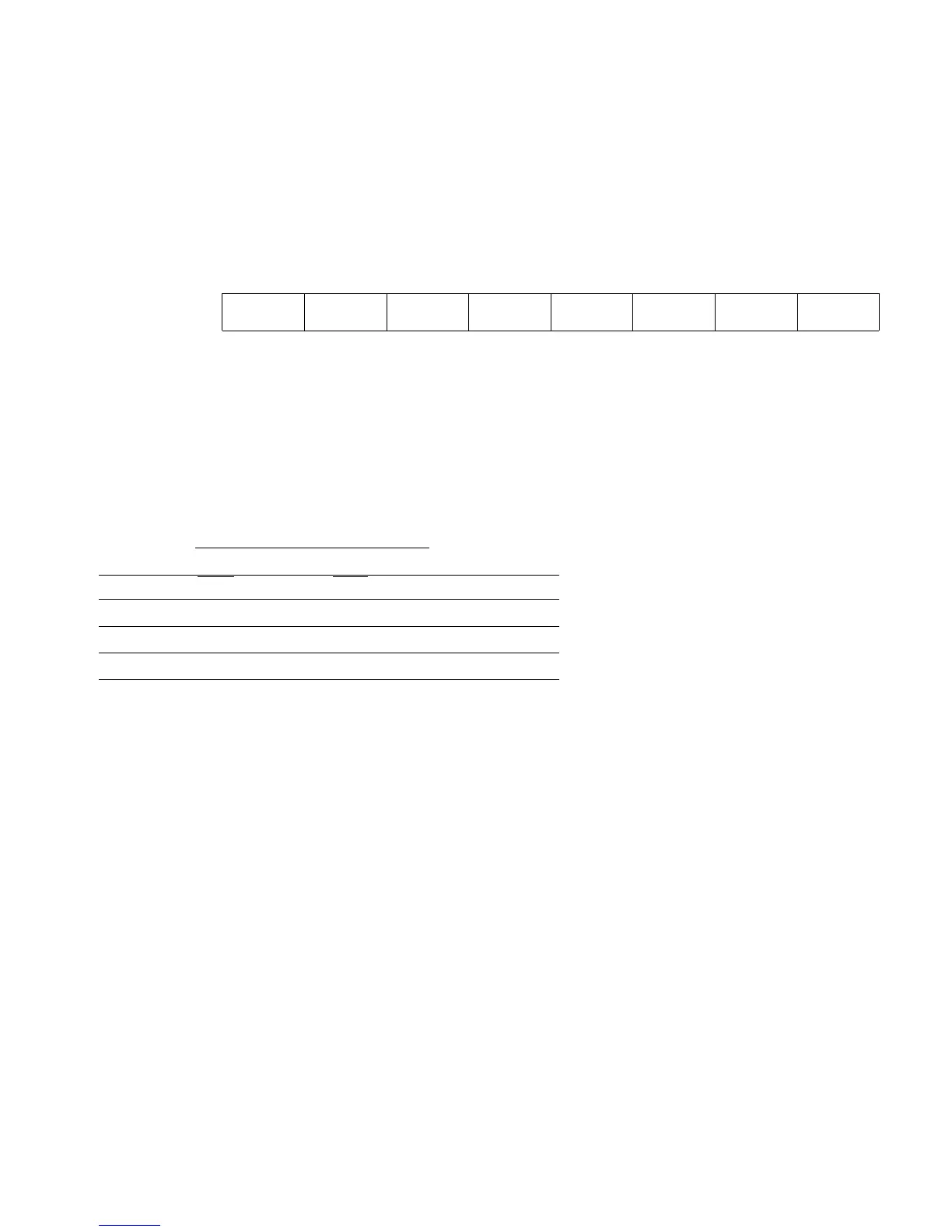

IRQ0, IRQ1, and the on-chip supporting modules are each assigned three bits in one of the four

interrupt priority registers (IPRA to IPRD). These bits specify a priority level from 7 (high) to 0

(low) for interrupts from the corresponding source. The drawing below shows the configuration

of the interrupt priority registers. Table 5-3 lists their assignments to interrupt sources.

Note: Bits 7 and 3 are reserved. They cannot be modified and are always read as “0.”

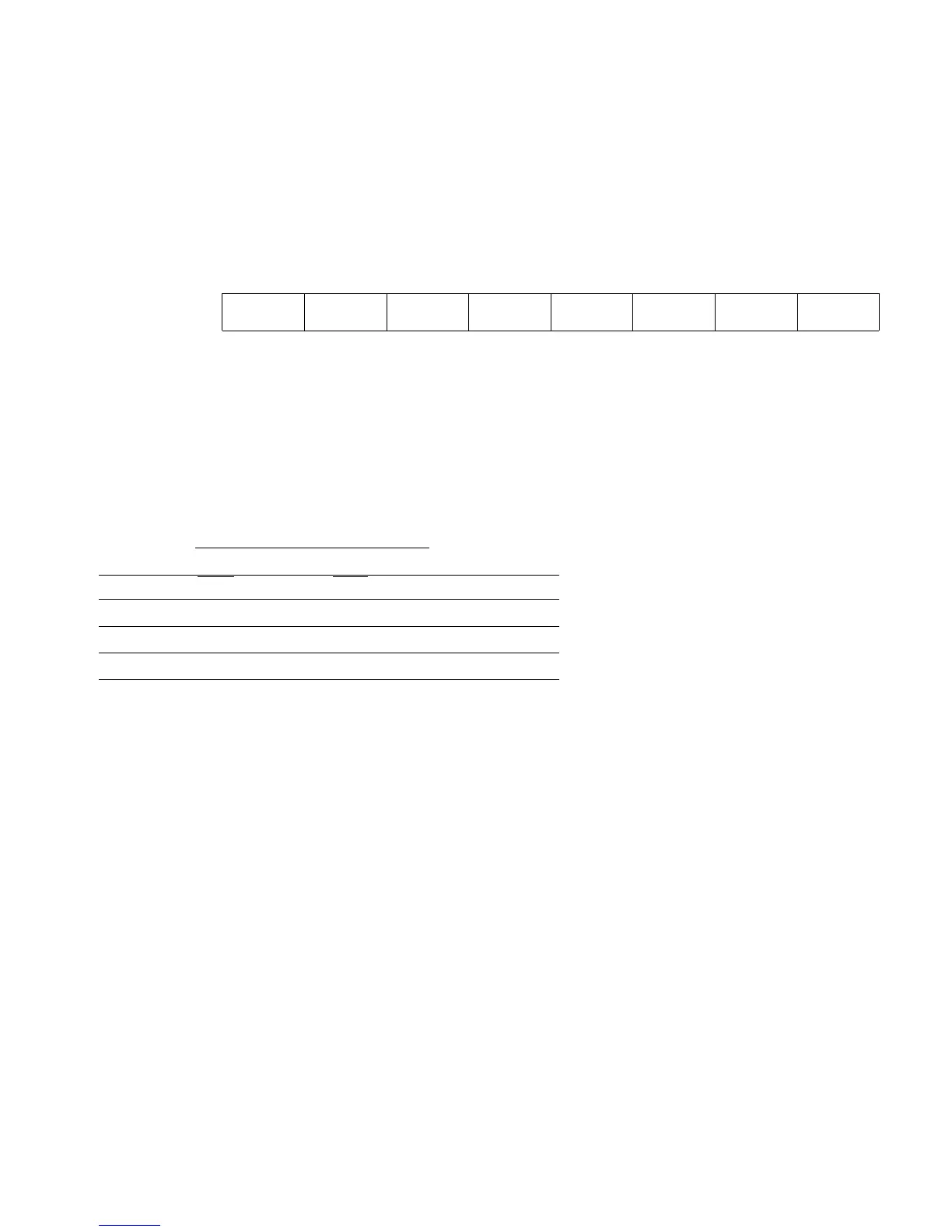

Table 5-3 Assignment of Interrupt Priority Registers

As table 5-3 indicates, each interrupt priority register specifies priority levels for two interrupt

sources. A user program can assign desired levels to these interrupt sources by writing “000” in

bits 6 to 4 or bits 2 to 0 to set priority level 0, for example, or “111” to set priority level 7.

A reset clears registers IPRA to IPRD to H'00, so all interrupts except NMI are initially masked.

Bit 76543210

——

Initial value 00000000

Read/Write R R/W R/W R/W R R/W R/W R/W

Interrupt Request Source

Register Bits 6 to 4 Bits 2 to 0 Address

IPRA IRQ

0 IRQ1 H'FFF0

IPRB 16-Bit FRT1 16-Bit FRT2 H'FFF1

IPRC 16-Bit FRT3 8-Bit timer H'FFF2

IPRD SCI A/D converter H'FFF3

103

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...