The data transfer count register is a 16-bit register that counts the number of bytes or words of

data remaining to be transferred. The initial count can be set from 1 to 65,536. A register value of

0 designates an initial count of 65,536.

The data transfer count register is decremented automatically after each byte or word is

transferred. When its value reaches 0, indicating that the designated number of bytes or words

have been transferred, a CPU interrupt is generated with the vector of the interrupt that requested

the data transfer.

6.2.5 Data Transfer Enable Registers A to D (DTEA to DTED)

These four registers designate whether an interrupt starts the DTC. The bits in these registers are

assigned to interrupts as indicated in table 6-3. No bits are assigned to the NMI, FOVI, OVI, and

ERI interrupts, which cannot request data transfers.

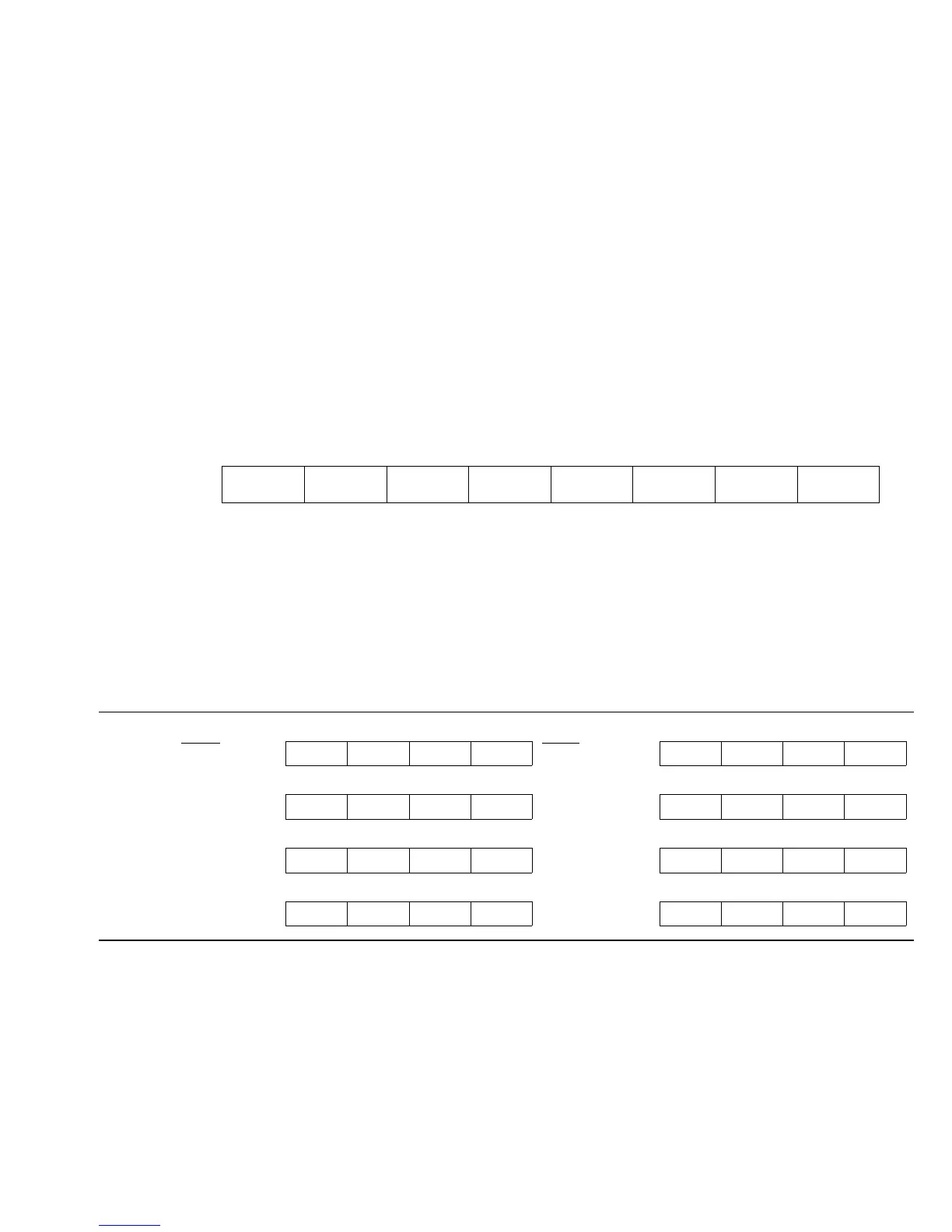

Table 6-3 Assignment of Data Transfer Enable Registers

Note: Bits marked “—” should always be cleared to “0.”

If the bit for a certain interrupt is set to “1,” that interrupt is regarded as a request for DTC service.

If the bit is cleared to “0,” the interrupt is regarded as a CPU interrupt request.

Only the 16 interrupts indicated in table 6-3 can request DTC service. DTE bits not assigned to

any interrupt (indicated by “—” in table 6-3) should be left cleared to “0.”

Bit 76543210

Initial value 00000000

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Interrupt Source Interrupt Source

Register Module Bits 7 to 4 Module Bits 3 to 0

7654 3210

DTEA IRQ

0 ———IRQ0 IRQ1 ———IRQ1

DTEB 16-Bit FRT1 — OCIB OCIA ICI 16-Bit FRT2 — OCIB OCIA ICI

DTEC 16-Bit FRT3 — OCIB OCIA ICI 8-Bit Timer — — CMIB CMIA

DTED SCI — TXI RXI — A/D converter — — — ADI

117

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...