15.2 Register Descriptions

15.2.1 A/D Data Registers (ADDR)—H'FFE0 to H'FFE7

The four A/D data registers (ADDRA to ADDRD) are 16-bit read-only registers that store the

results of A/D conversion.

Each result consist of 10 bits. The first 8 bits are stored in the upper byte of the data register

corresponding to the selected channel. The last two bits are stored in the lower data register byte.

Each data register is assigned to two analog input channels as indicated in table 15-3.

The A/D data registers are always readable by the CPU. The upper byte can be read directly. The

lower byte is read via a temporary register. See section 15-3, “CPU Interface” for details.

The unused bits (bits 5 to 0) of the lower data register byte are always read as 0.

The A/D data registers are initialized to H'0000 at a reset and in the standby modes.

Table 15-3 Assignment of Data Registers to Analog Input Channels

Analog Input Channel

Group 0 Group 1 A/D Data Register

AN

0 AN4 ADDRA

AN

1 AN5 ADDRB

AN

2 AN6 ADDRC

AN

3 AN7 ADDRD

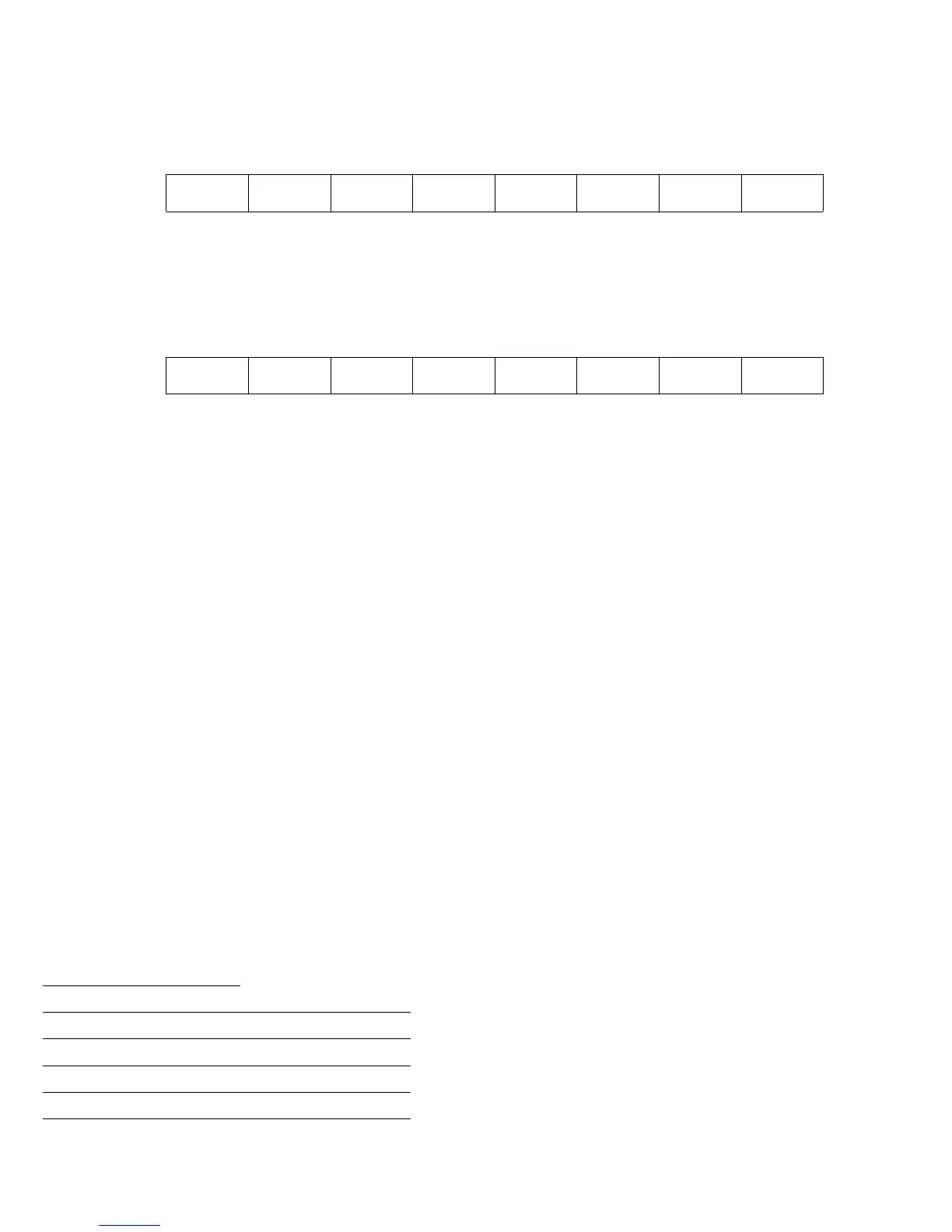

Bit 76543210

ADDRn H AD

9 AD8 AD7 AD6 AD5 AD4 AD3 AD2

Initial value 00000000

Read/Write RRRRRRRR

(n = A to D)

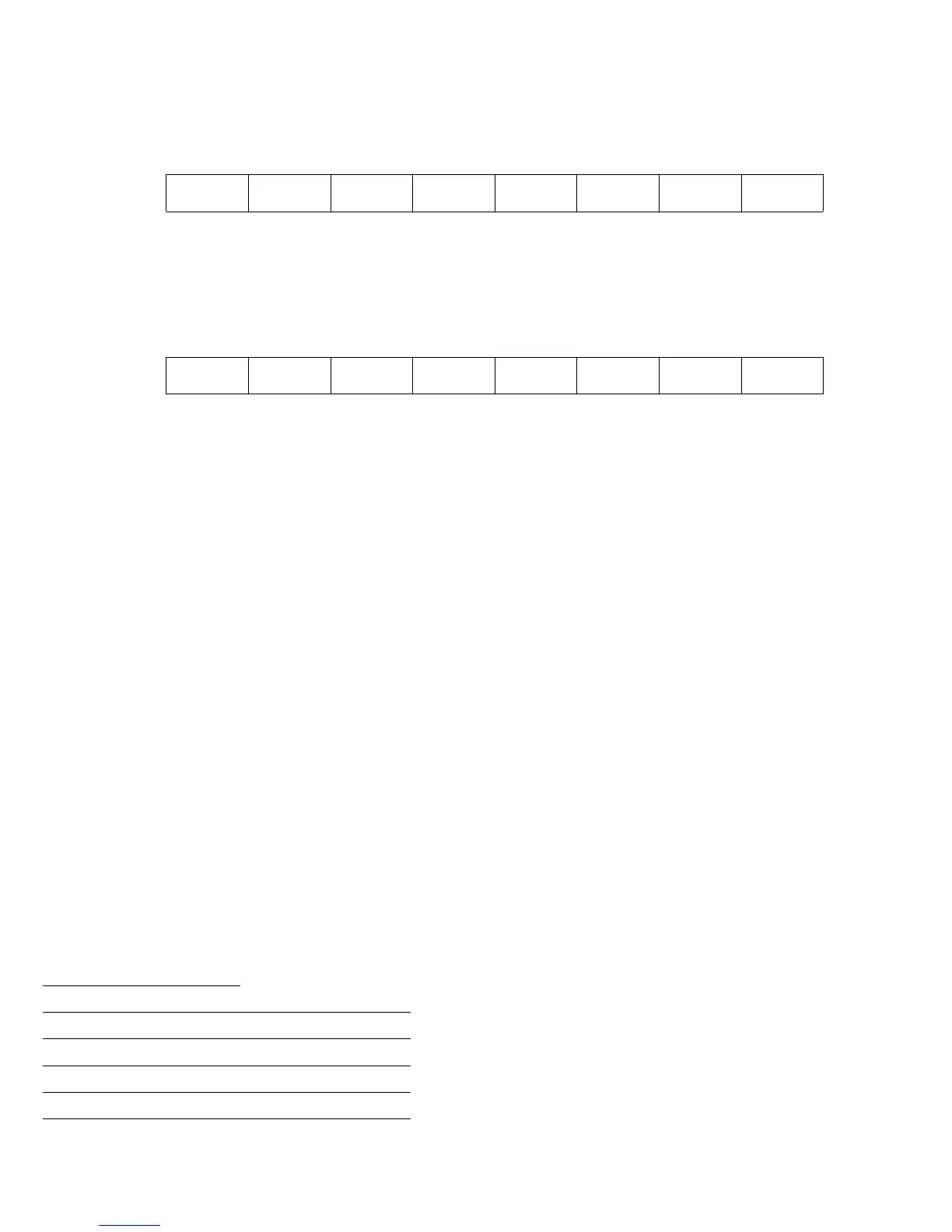

Bit 76543210

ADDRn H AD

1 AD0 ——————

Initial value 00000000

Read/Write RRRRRRRR

(n = A to D)

276

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...