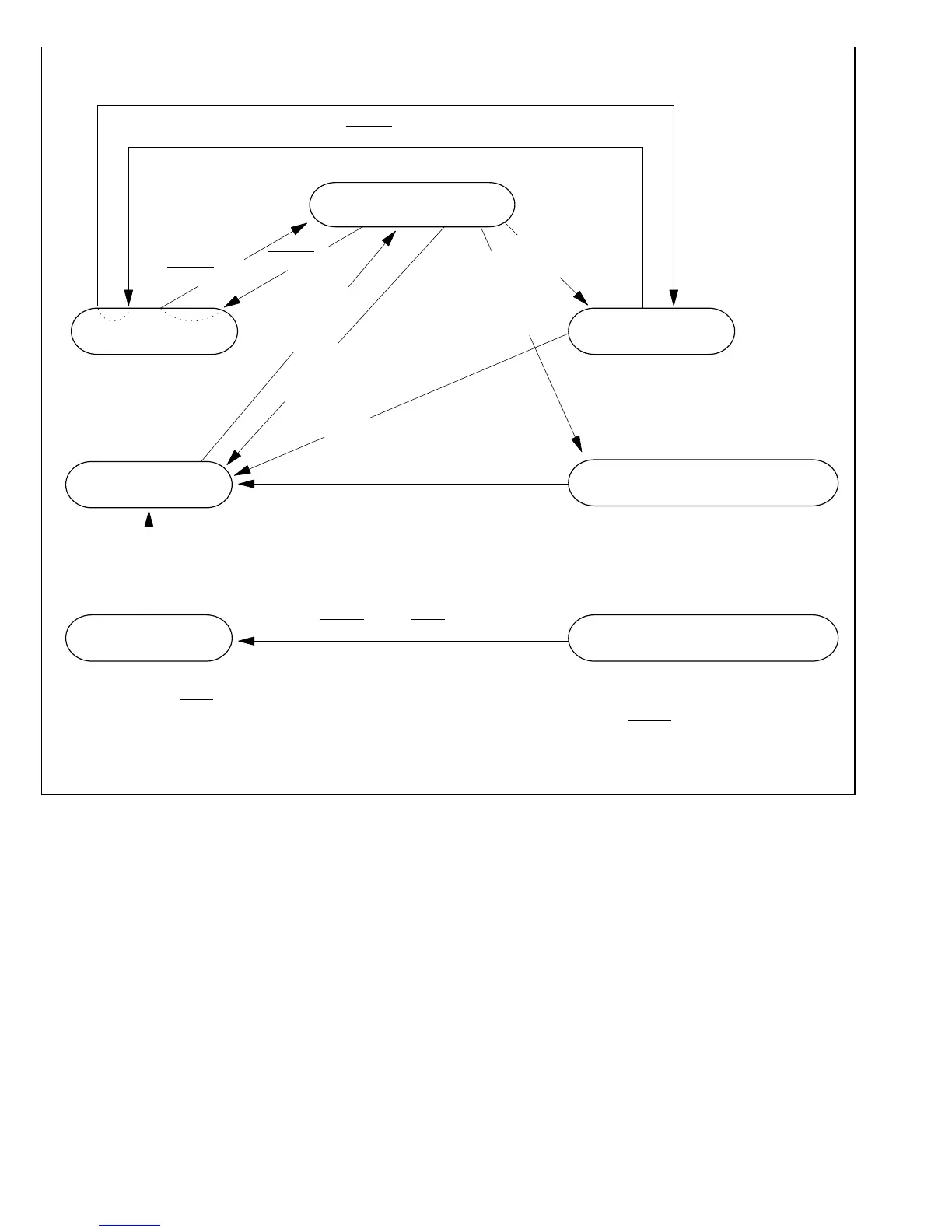

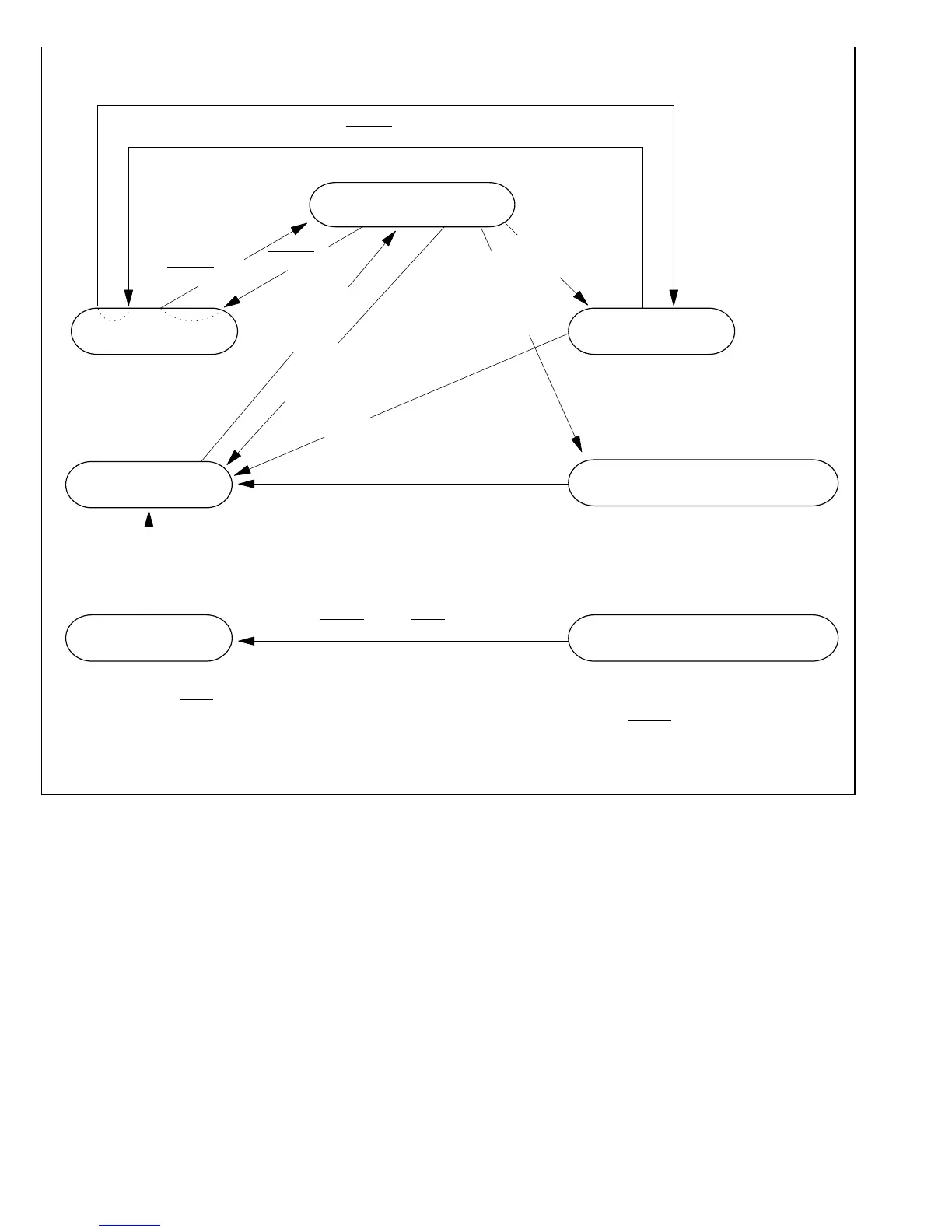

3.8.2 Program Execution State

In this state the CPU executes program instructions in normal sequence.

3.8.3 Exception-Handling State

The exception-handling state is a transient state that occurs when the CPU alters the normal

program flow due to an interrupt, trap instruction, address error, or other exception. In this state

the CPU carries out a hardware-controlled sequence that prepares it to execute a user-coded

exception-handling routine.

BREQ = “0”

BREQ = “0”

BREQ = “1”

Bus-released state

End of

exception

handling

Request

for exception

handling

SLEEP

instruction

with standby

flag set

SLEEP

instruction

Interrupt request

NMI

Program execution state

Exception-handling

state

Sleep mode

Software standby mode

Hardware standby mode

Reset state

*

STBY = “1”, RES = “0”

RES = “1”

* From any state except the hardware standby mode, a transition to the reset state occurs

whenever RES goes Low.

* A transition to the hardware standby mode from any state occurs when STBY goes Low.

BREQ = “1”

1 *2

1

2

Figure 3-12 State Transitions

71

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...