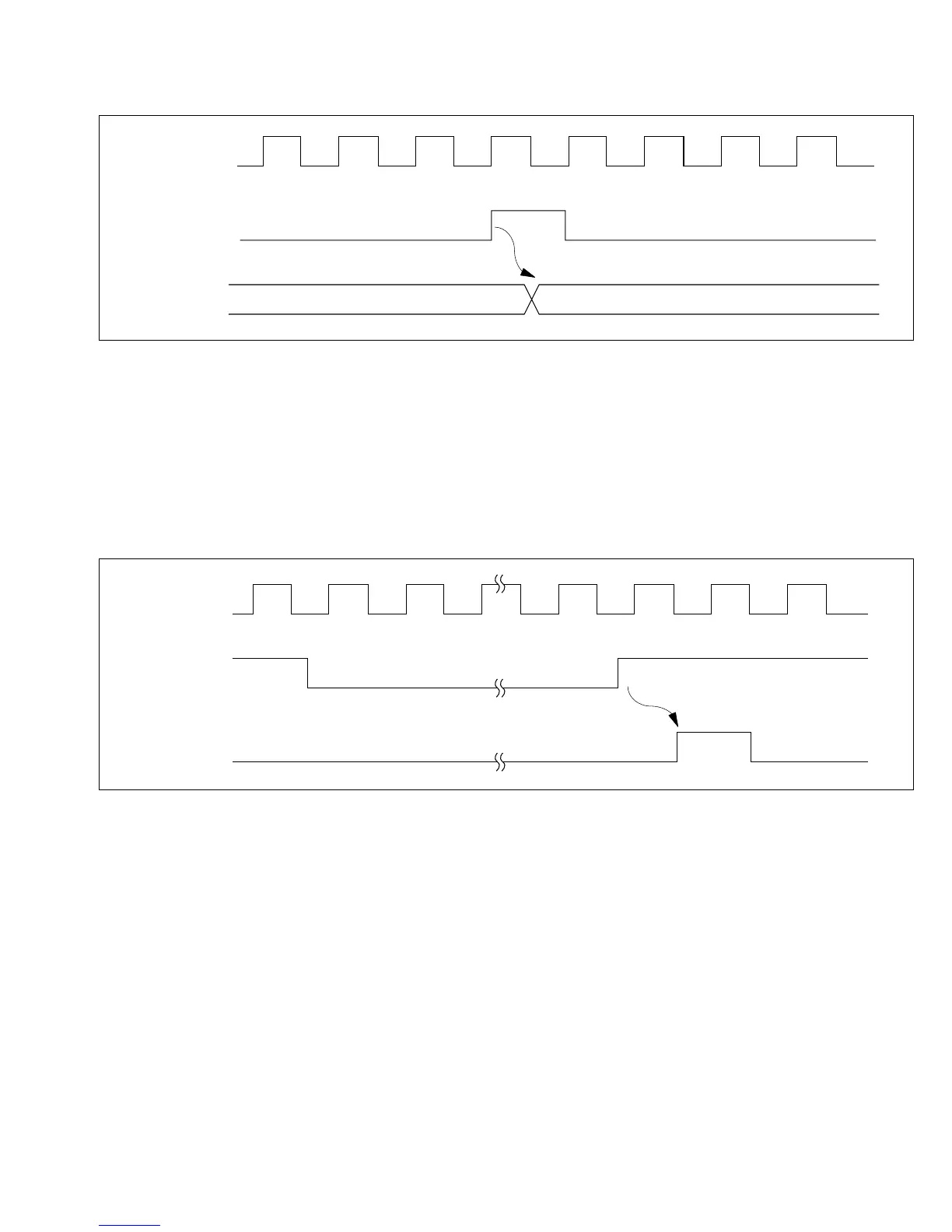

FRC Clear Timing: If the CCLRA bit is set to “1,” the FRC is cleared when compare-match A

occurs. Figure 10-6 shows the timing of this operation.

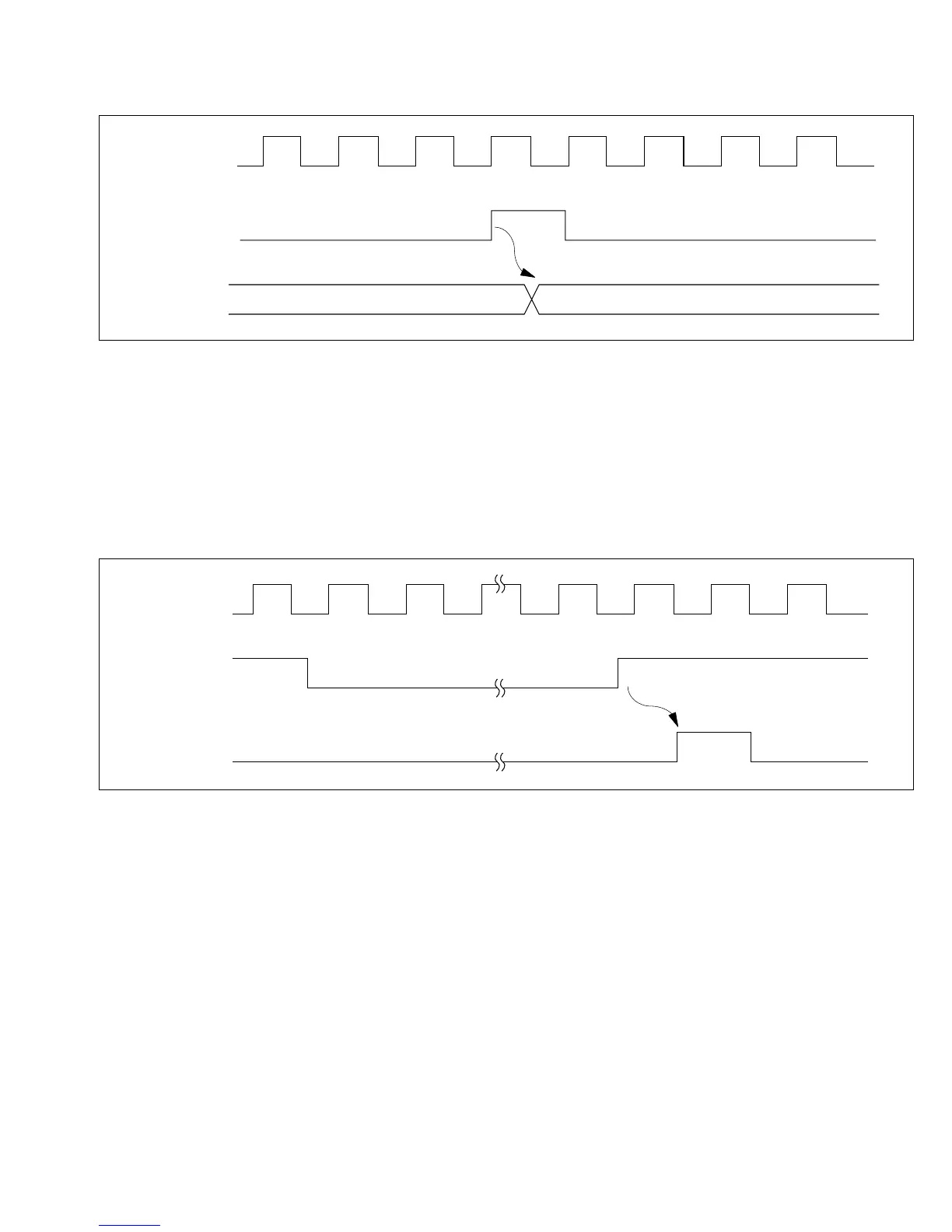

10.4.3 Input Capture Timing

1. Input Capture Timing: An internal input capture signal is generated from the rising or falling

edge of the input at the input capture pin (FTI), as selected by the IEDG bit in the TCSR.

Figure 10-7 shows the usual input capture timing when the rising edge is selected

(IEDG = “1”).

But if the upper byte of the ICR is being read when the input capture signal arrives, the internal

input capture signal is delayed by one state. Figure 10-8 shows the timing for this case.

Internal compare-

match A signal

FRC

ø

N H’0000

Input at FTI pin

Internal input

capture signal

ø

Figure 10-6 Clearing of FRC by Compare-Match A

Figure 10-7 Input Capture Timing (Usual Case)

193

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...