3.5.8 System Control Instructions

Table 3-16 describes the 12 system control instructions.

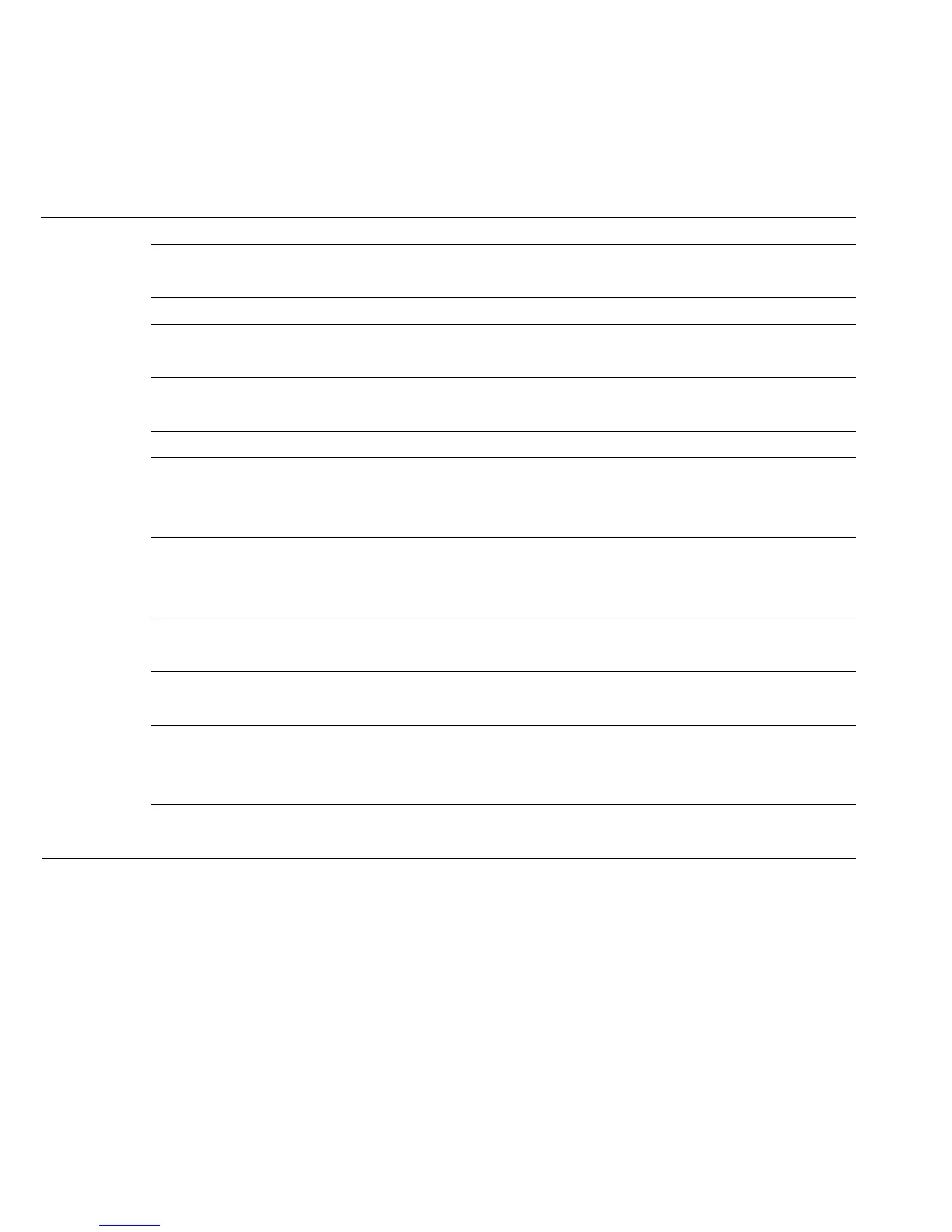

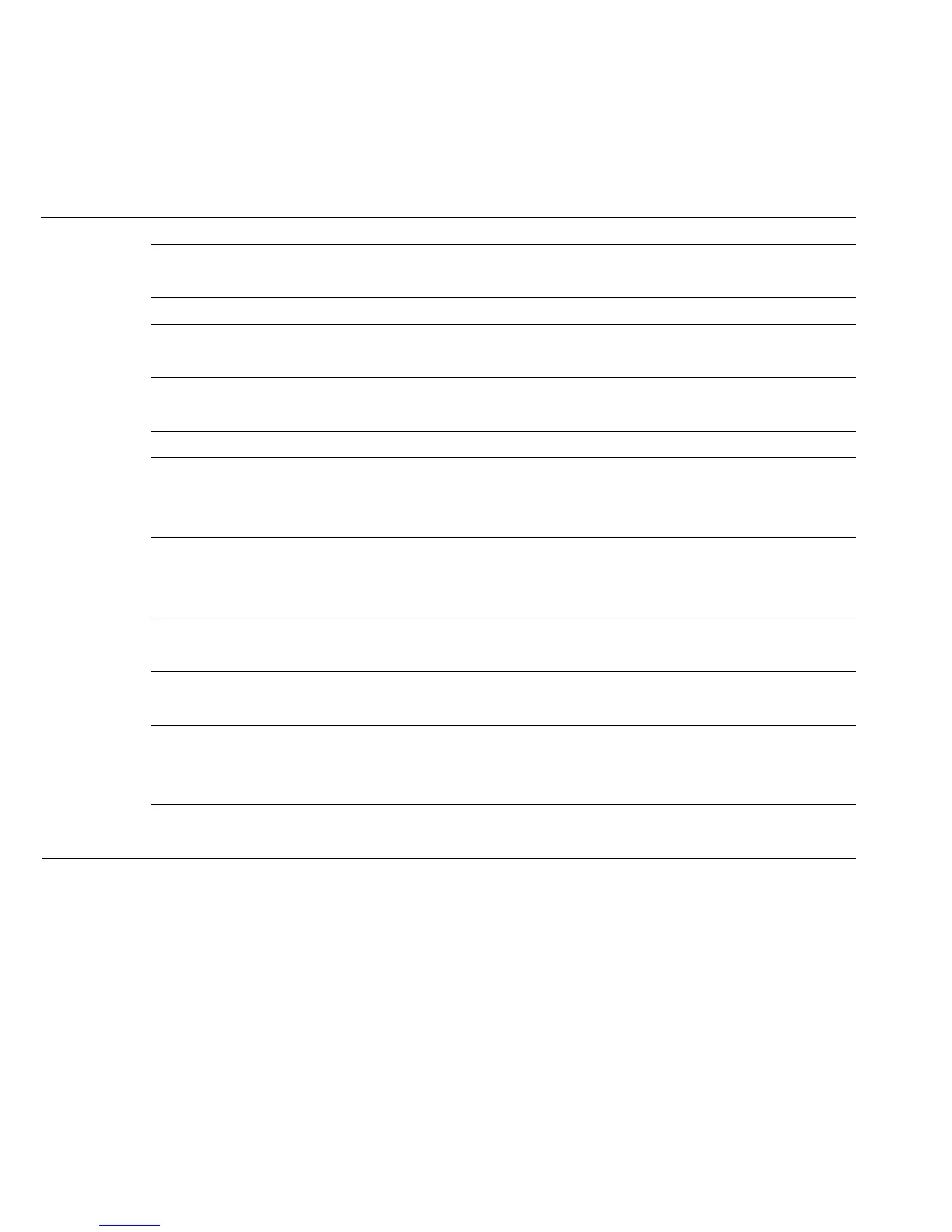

Table 3-16 System Control Instructions

Instruction Size Function

System TRAPA — Generates a trap exception with a specified vector number.

control TRAP/VS — Generates a trap exception if the V bit is set to “1” when

the instruction is executed.

RTE — Returns from an exception-handling routine.

LINK — FP → @–SP; SP → FP; SP + #IMM → SP

Creates a stack frame.

UNLK — FP → SP; @SP+ → FP

Deallocates a stack frame created by the LINK instruction.

SLEEP — Causes a transition to the power-down state.

LDC B/W* (EAs) → CR

Moves immediate data or general register or memory

contents to a specified control register.

STC B/W* CR → (EAd)

Moves control register data to a specified general register

or memory location.

ANDC B/W* CR ∧ #IMM → CR

Logically ANDs a control register with immediate data.

ORC B/W* CR ∨ #IMM → CR

Logically ORs a control register with immediate data.

XORC B/W* CR ⊕ #IMM → CR

Logically exclusive-ORs a control register with immediate

data.

NOP — PC + 1 → PC

No operation. Only increments the program counter.

* The size depends on the control register.

When using the LDC and STC instructions to stack and unstack the BR, CCR, TP, DP, and EP

control registers in the H8/500 family, note the following point.

H8/500 hardware does not permit byte access to the stack. If the LDC.B or STC.B assembler

mnemonic is coded with the @R7 + (@SP+) or @–R7 (@–SP) addressing mode, the stack-

pointer addressing mode takes precedence and hardware automatically performs word access.

59

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...