Instruction

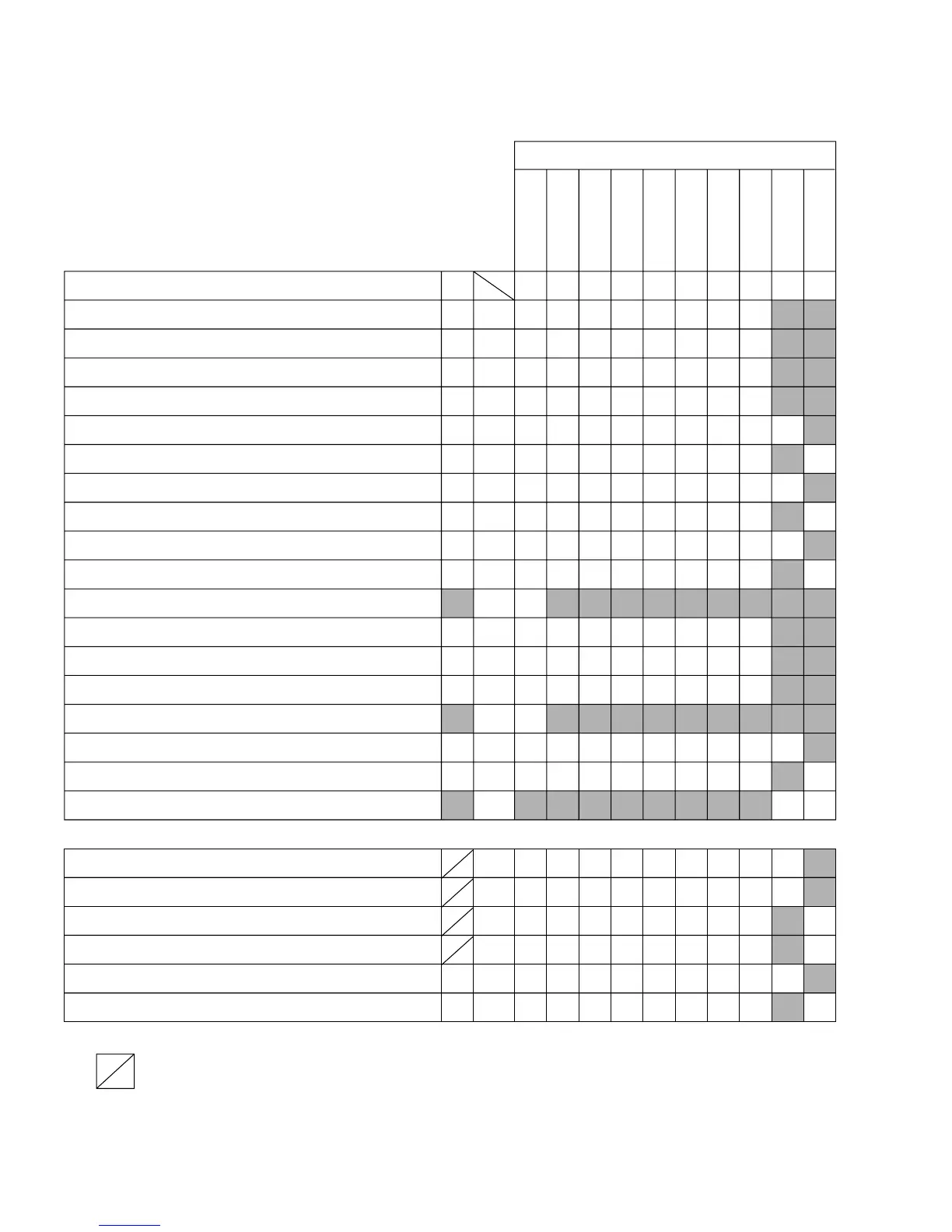

Rn

@Rn

@(d:8, Rn)

@(d:16, Rn)

@–Rn

@Rn+

@aa:8

@aa:16

#xx:8

#xx:16

Addressing mode

SHLR.B

SHLR.W

STC.B

STC.W

SUB.B

SUB.W

SUBS.B

SUBS.W

SUBX.B

SUBX.W

SWAP

TAS

TST.B

TST.W

XCH

XOR.B

XOR.W

XORC

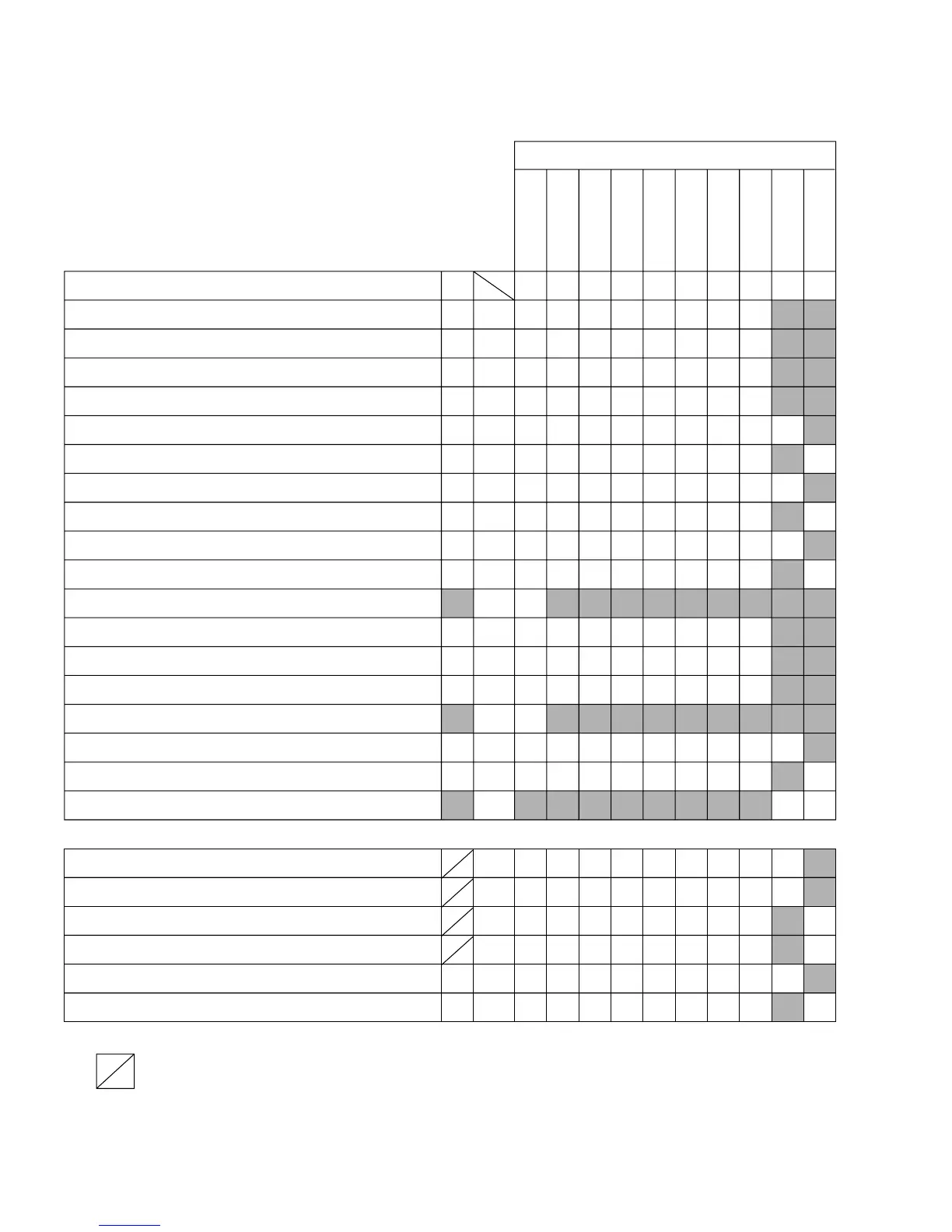

DIVXU.B

DIVXU.B

DIVXU.W

DIVXU.W

DIVXU.B

DIVXU.W

2 1 27787

8

78

1

J

11231

1

232

K

3

412

1 1 27787

8

78

2 1 27787

8

78

1 1 25565

6

563

2 1 25565

6

56 4

1 1 35565

6

563

2 1 35565

6

56 4

1 1 25565

6

563

2 1 25565

6

56 4

1

95

2 1 47787

8

78

1 1 25565

6

56

2 1 25565

6

56

14

112

414

1

6

1 2023232423

24

23 24

1 2528282928

29

28 29

1 2023232423

24

23 24 27

1 2528282928

29

28 29 27

1 1 11 11 12 11

12

11 12

2 1 11 11 12 11

12

11 12

Zero divide, minimum mode

Zero divide, maximum mode

Zero divide, minimum mode

Zero divide, maximum mode

Overflow

Overflow

21

21

8

8

9

10

7

10

12

6

8

10

11

7787

8

78

3

5565

6

56

5565

6

56

3

4

For register and immediate

operands

For memory operand

↵

*

↵

*

Loading...

Loading...