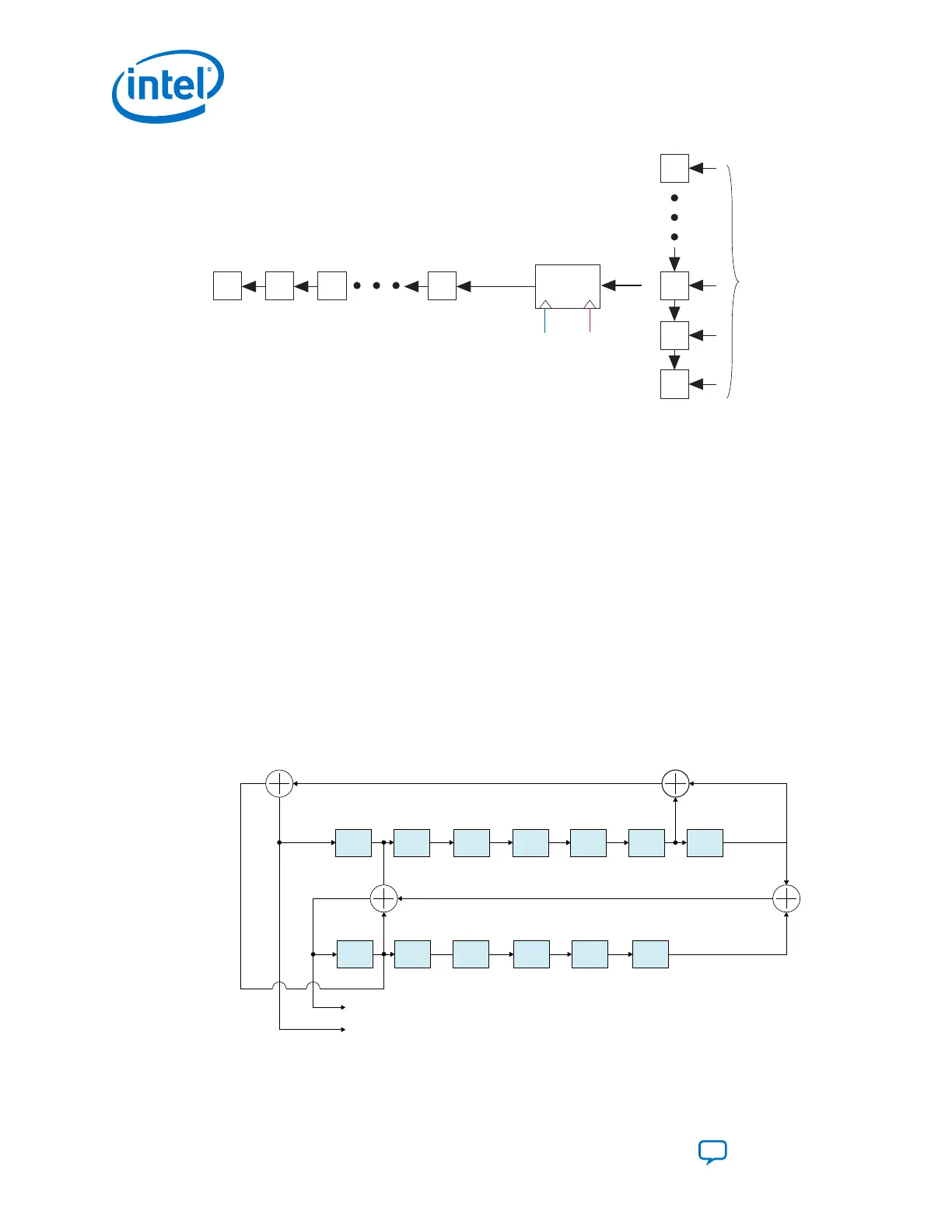

Dn

D2

D1

D0

Parallel

Data

Serializer

DnD2D1D0

Parallel

Clock

Serial

Clock

Serial

Data

LSB

3.1.1.4. Data Pattern Generation

The data pattern generator is a Design for Test (DFT) feature capable of generating

data traffic for the PHY to debug the PMA without involving the upper protocol stack

layers.

The Intel Stratix 10 E-Tile has an on-chip pseudo random pattern generation block

that operates in all bit modes and can generate several patterns. In addition to this, it

can generate an 80-bit user-defined pattern.

There are patterns supporting both NRZ and PAM4. Pseudo random bit sequence

(PRBS) NRZ patterns are different from PAM4 patterns. Different specifications such as

CEI OIF and IEEE 803.2, refer to quaternary PAM4 patterns differently. QPRBS13 is

identical to PRBSQ13 and QPRBS31 is identical to PRBSQ31.

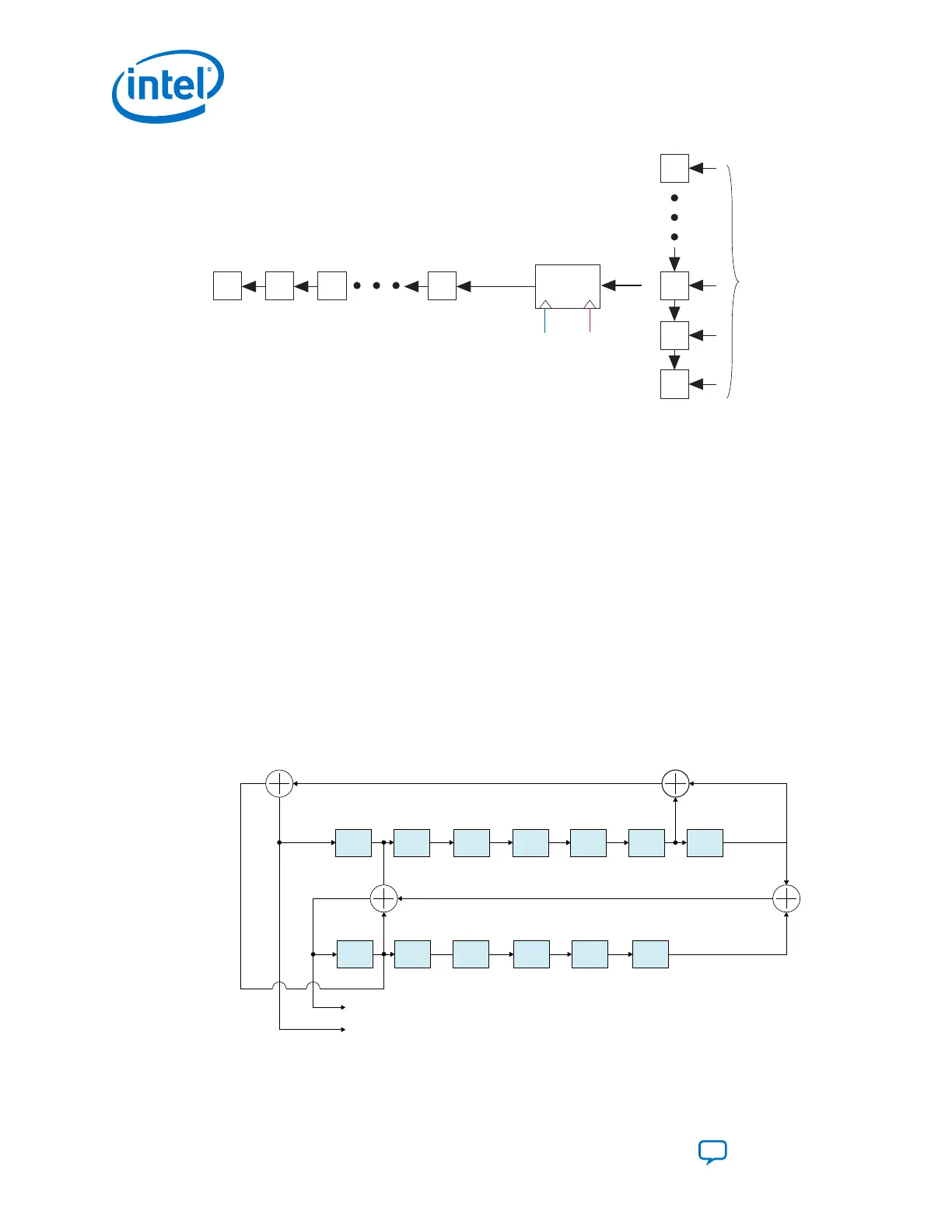

As defined in OIF Clause 16: CEI-56G-VSR-PAM4 Very Short Reach Interface

specifications, typically, each cycle of PRBSQ13 is 8191 unique symbols long. Each

cycle is formed by gray coding and PAM4 encoding of bits from two repetitions of the

PRBS13 pattern and used for transmitter compliance testing.

Figure 35. QPRBS13-CEI Pattern

S0 S2 S4 S6 S8 S10 S12

S1 S3 S5 S7 S9 S11

B (msb)

A (lsb)

QPRBS13-CEI pattern outputs to

Gray coding and PAM4 coding

3. Intel Stratix 10 E-Tile Transceiver PHY Architecture

UG-20056 | 2019.02.04

Intel

®

Stratix

®

10 E-Tile Transceiver PHY User Guide

Send Feedback

62

Loading...

Loading...