Because RFL™ and Hubbell® have a policy of continuous product improvement, we reserve the right to change designs and specifications without notice.

2.3.3.4 Multiplexing Of Channels To Form T1 Aggregate

The multiplexer develops backplane bus synchronization signals. The transmit section of each channel

module synchronizes to these signals, and places its data onto the selected bus. The multiplexer then

forms the aggregate signal, using the selected framing format (SF or ESF).

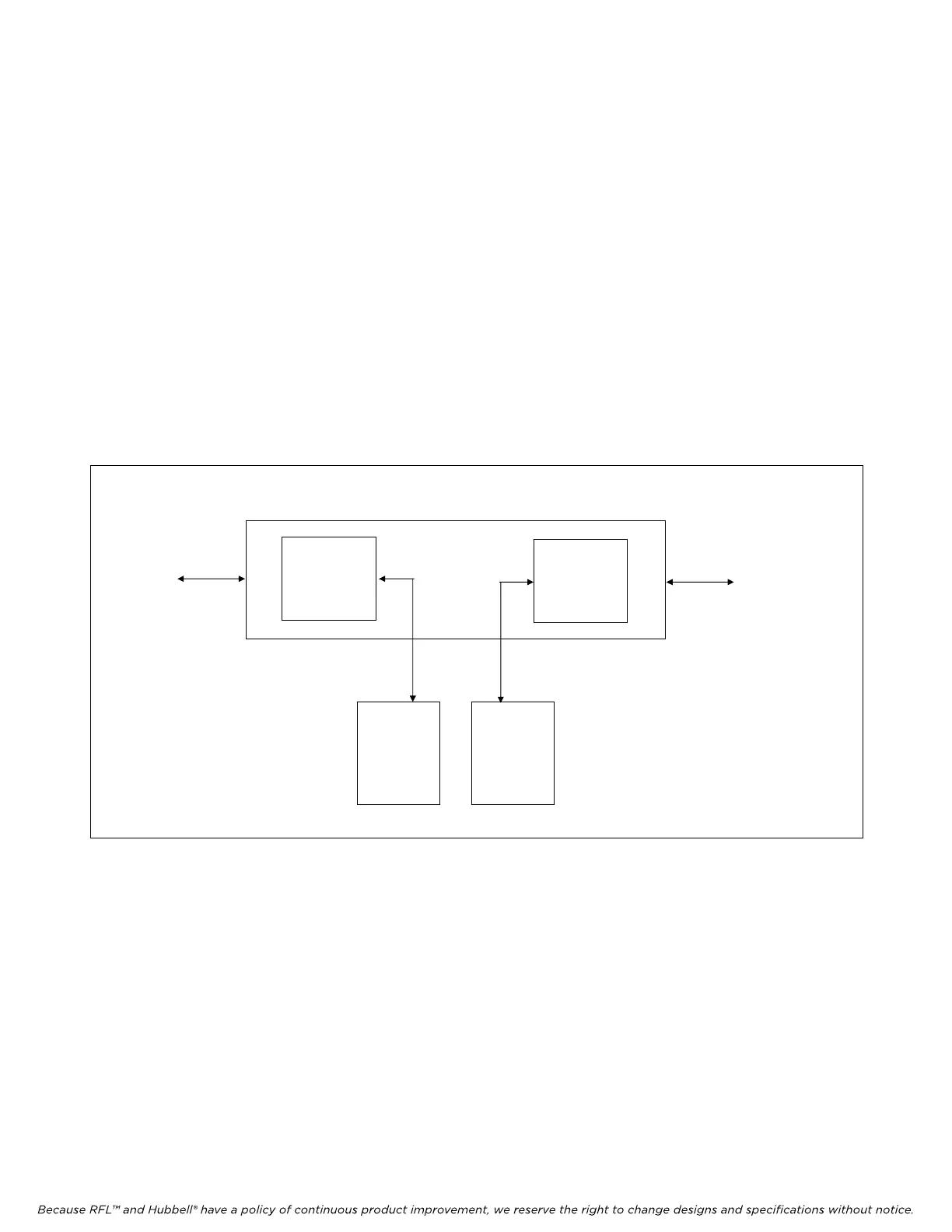

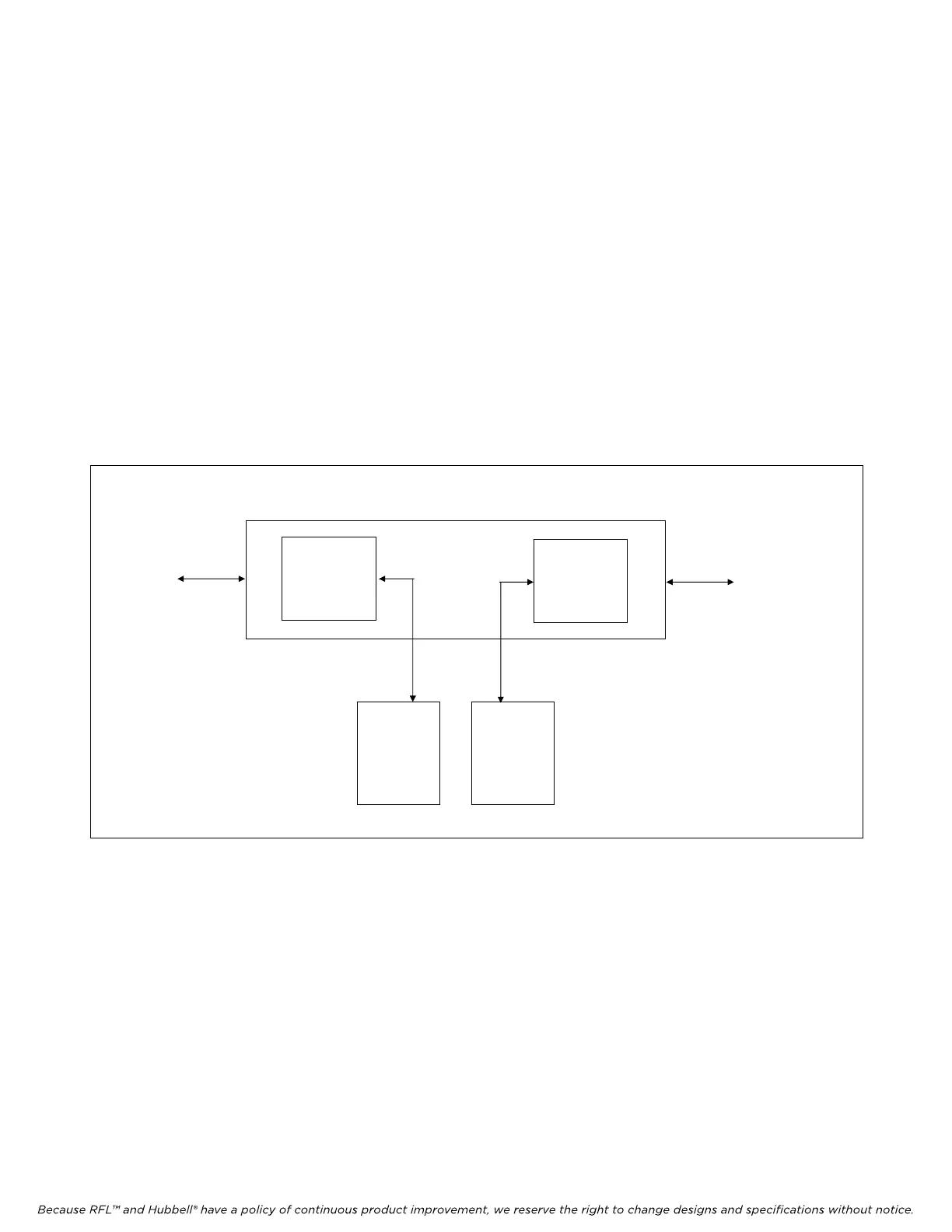

2.3.3.5 Multiplexer/Demultiplexer Bus Interface To Channels

The CM4 uses tri-state bus drivers and receivers to permit routing the demultiplexer and multiplexer

bus signals to either of two backplane buses (Bus A or Bus B). This versatile bus capability enables

simple configuration of a multiplexer as a "drop/insert."

Bus A/B nomenclature is used to set channel modules to transmit and receive through a desired drop-

and-insert port. In order to transmit out of drop-and-insert A, a channel module is set to operate on Bus

A. In order to transmit out of drop-and-insert B, a channel module is set to operate on Bus B. This can

be seen in Figure 2-16.

DI/A

DI/B

CHANNEL

MODULE

SET TO

BUS B

CHANNEL

MODULE

SET TO

BUS A

Figure 2-16. The meaning of Bus A and Bus B channel module settings

2.3.3.6 Transmit Timing Functions

The CM4 enables the selection of LOOP, INTERNAL, EXTERNAL, or THRU timing. In addition to

primary timing, the CM4 provides a fallback timing setting. Fallback timing takes effect automatically

when conditions cause a loss of primary timing; for example, in case of frame loss when LOOP is the

primary timing setting. Refer to paragraph 5.5.3.7.1.1 for suggested settings of fallback timing.

M-DACS-T1 RFL Electronics Inc.

October 16, 2012 2-30 (973) 334-3100

Loading...

Loading...